Distributed by:

# www.Jameco.com + 1-800-831-4242

The content and copyrights of the attached material are the property of its owner.

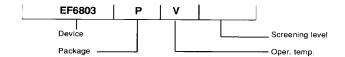

EF6801 EF6803

# MICROCOMPUTER/MICROPROCESSOR (MCU/MPU)

- ENHANCED EF6800 INSTRUCTION SET

- 8 X 8 MULTIPLY INSTRUCTION

- SERIAL COMMUNICATIONS INTERFACE (SCI)

- UPWARD SOURCE AND OBJECT CODE COMPATIBILITY WITH THE 6800

- 16-BIT THREE-FUNCTION PROGRAMMABLE TIMER

- SINGLE-CHIP OR EXPANDED OPERATION TO 64K BYTE ADDRESS SPACE

- BUS COMPATIBILITY WITH THE 6800 FAMILY

- 2048 BYTES OF ROM (EF6801)

- 128 BYTES OF RAM

- 64 BYTES OF RAM RETAINABLE DURING POWERDOWN

- 29 PARALLEL I/O AND TWO HANDSHAKE CONTROL LINES

- INTERNAL CLOCK GENERATOR WITH DIVIDE-BY-FOUR OUTPUT

- -40°C TO +85°C TEMPERATURE RANGE

- - 40°C TO + 105°C TEMPERATURE RANGE

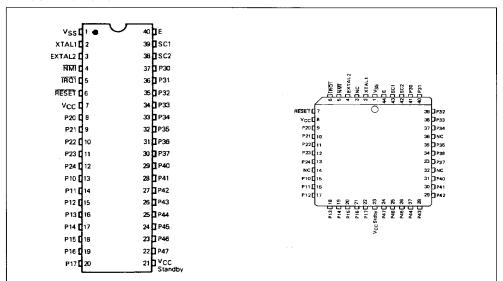

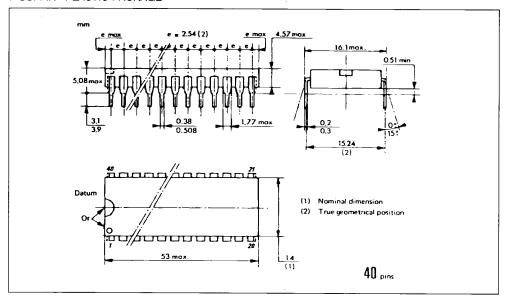

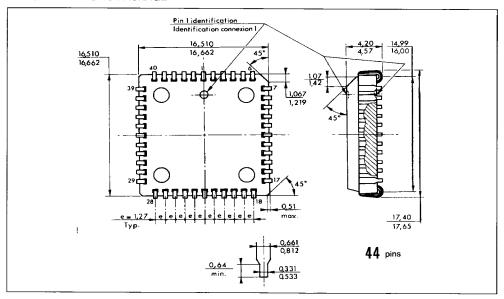

## PIN CONNECTIONS

May 1989

1/49

#### DESCRIPTION

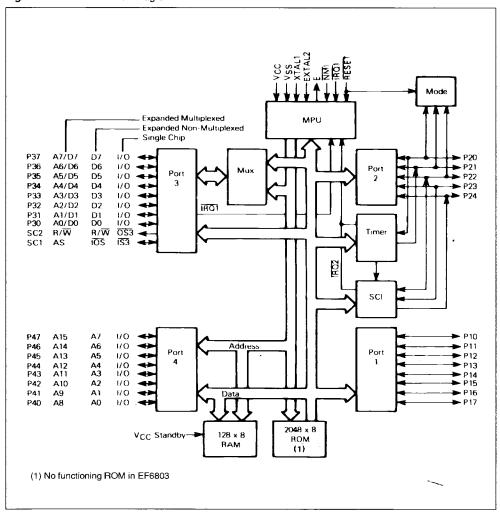

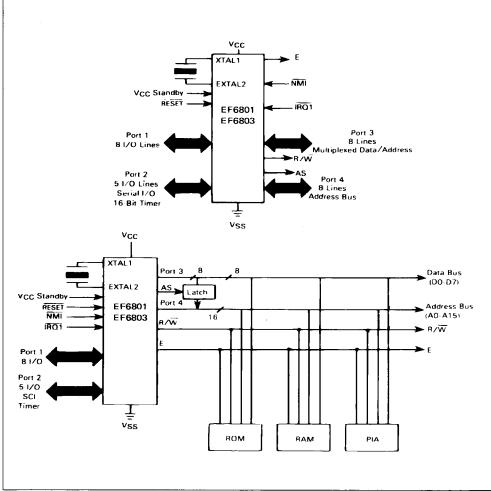

The EF6801 is an 8-bit single-chip microcomputer unit (MCU) which significantly enhances the capabilities of the 6800 family of parts. It includes an upgraded 6800 microprocessor unit (MPU) with upward-source and object-code compatibility. Execution times of key instructions have been improved and several new instructions have been added including an unsigned multiply. The MCU can

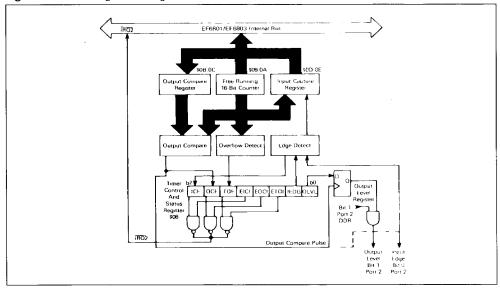

Figure 1: 6801/6803 Bock Diagram.

function as a monolithic microcomputer or can be expanded to a 64K byte address space. It is TTL compatible and requires one + 5V power supply. On-chip resources include 2048 bytes of ROM, 128 bytes of RAM, a Serial Communications Interface (SCI), parallel I/O, and a three function Programmable Timer. The EF6803 can be considered as an EF6801 operating in Modes 2 or 3. EF6801 MCU Family features include:

#### POWER CONSIDERATIONS

The average chip-junction temperature,  $T_J$ , in  $^{\circ}C$  can be obtained from :

$$T_{J} = T_{A} + (P_{D} \cdot \theta_{JA}) \tag{1}$$

Where:

$\theta_{JA}$   $\equiv$  Package Thermal Resistance, Junction -to-Ambient,  $^{\circ}$ C/W

PD = PINT + PPORT

P<sub>INT</sub> = I<sub>CC</sub> x V<sub>CC</sub>, Watts - Chip Internal Power

$P_{PORT} \equiv Port Power Dissipation, Watts - User Determined$

For most applications PPORT<< PINT and can be neglected. PPORT may become significant if the device is configured to drive Darlington bases or sink LED

An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{PORT}$  is neglected) is :

$$P_D = K + (T_J + 273^{\circ}C)$$

(2)

Solving equations 1 and 2 for K gives:

$$K = PD \cdot (T_{A+} 273^{\circ}C) + \theta_{JA} \cdot P_{D}^{2}$$

(3)

Where K is a constant pertaining to the particular part. K can be determined from equation 3 by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K the values of  $P_D$  and  $T_J$  can be obtained by solving equations (1) and (2) iteratively for any value of  $T_A$ .

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                                                                                                                                               | Value                                                                    | Unit |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------|

| Vcc              | Supply Voltage                                                                                                                                          | - 0.3 to + 7.0                                                           | ٧    |

| Vin              | Input Voltage                                                                                                                                           | - 0.3 to + 7.0                                                           | V    |

| TA               | Operating Temperature Range<br>EF6801/03, EF6801/03-1, EF68A01/03, EF68B01/03<br>EF6801/03, EF6801/03-1 : V Suffix<br>EF6801/03, EF6801/03-1 : A Suffix | T <sub>L</sub> to T <sub>H</sub><br>0 to 70<br>- 40 to 85<br>- 40 to 105 | ℃    |

| T <sub>stg</sub> | Storage Temperature Range                                                                                                                               | - 55 to + 150                                                            | °C   |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high-impedance circuit. For proper operation it is recommended that  $V_{IN}$  and  $V_{Out}$  be constrained to the range  $V_{SS} \le \{V_{in} \text{ or } V_{out}\} \le V_{CC}$ . Input protection is enhanced by connecting unused inputs to either  $V_{DD}$  or  $V_{SS}$ .

#### THERMAL DATA

| θ <sub>JA</sub> | Thermal Resistance | Plastic | 50  | °C/W | ĺ |

|-----------------|--------------------|---------|-----|------|---|

|                 |                    | PLCC    | 100 |      | ı |

# **CONTROL TIMING** $(V_{CC} = 5.0V \pm 5\%, V_{SS} = 0, T_A = 0 \text{ to } 70^{\circ}\text{C})$

| Symbol            | Parameter                        | EF6801 |      | EF6801-1 |      | EF68A01 |      | EF68B01 |      | Unit |

|-------------------|----------------------------------|--------|------|----------|------|---------|------|---------|------|------|

| Symbol            | Farameter                        | Min.   | Max. | Min.     | Max. | Min.    | Max. | Min.    | Max. | ]    |

| fo                | Frequency of Operation           | 0.5    | 1.0  | 0.5      | 1.25 | 0.5     | 1.5  | 0.5     | 2.0  | MHz  |

| f <sub>XTAL</sub> | Crystal Frequency                | 2.0    | 4.0  | 2.0      | 5.0  | 2.0     | 6.0  | 2.0     | 8.0  | MHz  |

| 4 <sub>fo</sub>   | External Oscillator Frequency    | 2.0    | 4.0  | 2.0      | 5.0  | 2.0     | 6.0  | 2.0     | 8.0  | MHz  |

| trc               | Crystal Oscillator Start Up Time |        | 100  |          | 100  |         | 100  |         | 100  | ms   |

| tecs              | Processor Control Setup Time     | 200    |      | 170      |      | 140     |      | 110     |      | ns   |

# DC ELECTRICAL CHARACTERISTICS

(V<sub>CC</sub> = 5.0Vdc  $\pm$  5%, V<sub>SS</sub> = 0, T<sub>A</sub> = T<sub>L</sub> to T<sub>H</sub> unless otherwise noted)

| Symbol                              | Parameter                                                                                    |                                                | 01/03<br>+ 70°C                    | EF68<br>- 40<br>+ 85°C/                        | Unit                               |    |

|-------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------|------------------------------------------------|------------------------------------|----|

|                                     |                                                                                              | Min.                                           | Max.                               | Min.                                           | Max.                               |    |

| V <sub>IH</sub>                     | Input High Voltage RESET Other Inputs                                                        | V <sub>SS</sub> + 4.0<br>V <sub>SS</sub> + 2.0 | V <sub>cc</sub><br>V <sub>cc</sub> | V <sub>SS</sub> + 4.0<br>V <sub>SS</sub> + 2.2 | V <sub>cc</sub><br>V <sub>cc</sub> | ٧  |

| VIL                                 | Input Low Voltage All Inputs                                                                 | V <sub>SS</sub> - 0.3                          | V <sub>SS</sub> + 0.8              | V <sub>SS</sub> - 0.3                          | V <sub>SS</sub> + 0.8              | ٧  |

| I <sub>in</sub>                     | Input Load Current (V <sub>in</sub> = 0 to 2.4V) Port 4<br>SCI                               |                                                | 0.5<br>0.8                         |                                                | 0.8<br>1.0                         | mA |

| l <sub>in</sub>                     | Input Leakage Current (V <sub>in</sub> = 0 to 5.25V) NMI, IRQ1, RESET                        |                                                | 2.5                                |                                                | 5.0                                | μA |

| I <sub>TSI</sub>                    | Hi-Z (off-state) Input Current<br>(V <sub>in</sub> = 0.5 to 2.4V) Ports 1, 2, and 3          |                                                | 10                                 |                                                | 20                                 | μΑ |

| V <sub>OH</sub>                     | Output High Voltage $\{I_{Load} = -65\mu^*, V_{CC} = Min\}^* E$ , Port 4, SC1, SC2           | V <sub>SS</sub> + 2.4                          |                                    | V <sub>SS</sub> + 2.4                          |                                    | ٧  |

|                                     | $(I_{Load} = -100\mu A, V_{CC} = Min)$ Other Outputs                                         | V <sub>SS</sub> + 2.4                          |                                    | V <sub>SS</sub> + 2.4                          |                                    |    |

| Vol                                 | Output Low Voltage $(I_{Load} = 2.0 \text{mA}, V_{CC} = \text{Min})$ All Outputs             |                                                | V <sub>SS</sub> + 0.5              |                                                | V <sub>SS</sub> + 0.6              | ٧  |

| loh                                 | Darlington Drive Current (V <sub>O</sub> = 1.5V) Port 1                                      | 1.0                                            | 4.0                                | 1.0                                            | 5.0                                | mA |

| P <sub>INT</sub>                    | Internal Power Dissipation (measured at $T_A = T_L$ in steady-state operation)               |                                                | 1200                               |                                                | 1500                               | mW |

| Cin                                 | Input Capacitance $(V_{in}=0, T_A=25^{\circ}C, f_o=1.0MHz)$ Port 3, Port 4, SC1 Other Inputs |                                                | 12.5<br>10                         |                                                | 12.5<br>10                         | pF |

| V <sub>SBB</sub><br>V <sub>SB</sub> | V <sub>CC</sub> Standby Powerdown Powerup                                                    | 4.0<br>4.75                                    | 5.25<br>5.25                       | 4.0<br>4.75                                    | 5.25<br>5.25                       | ٧  |

| I <sub>SBB</sub>                    | Standby Current Powerdown                                                                    |                                                | 6.0                                |                                                | 8.0                                | mA |

<sup>\*</sup> Negociable to -100µA (for further information contact the factory)

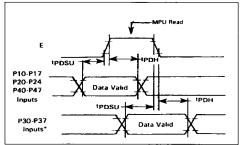

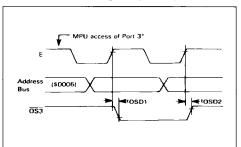

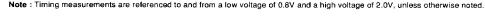

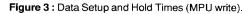

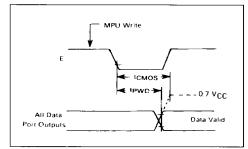

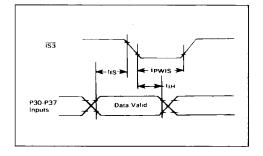

# PERIPHERAL PORT TIMING (refer to figures 2-5)

| Symbol            | Parameter                                                            |      |      |      | EF6801-1<br>EF6803-1 |      |      |      |      |    |

|-------------------|----------------------------------------------------------------------|------|------|------|----------------------|------|------|------|------|----|

|                   |                                                                      | Min. | Max. | Min. | Max.                 | Min. | Max. | Min. | Max. |    |

| tposu             | Peripheral Data Setup Time                                           | 200  |      | 200  |                      | 150  |      | 100  |      | ns |

| t <sub>PDH</sub>  | Peripheral Data Hold Time                                            | 200  |      | 200  |                      | 150  |      | 100  |      | ns |

| tosp1             | Delay Time, Enable Positive Transition to OS3<br>Negative Transition |      | 350  |      | 350                  |      | 300  |      | 250  | ns |

| tosp2             | Delay Time, Enable Positive Transition to OS3 Positive Transition    |      | 350  |      | 350                  |      | 300  |      | 250  | ns |

| tewo              | Delay Time, Enable Negative Transition to<br>Peripheral Data Valid   |      | 350  |      | 350                  |      | 300  |      | 250  | ns |

| t <sub>CMOS</sub> | Delay Time, Enable Negative Transition to Peripheral CMOS Data Valid |      | 2.0  |      | 2.0                  |      | 2.0  |      | 2.0  | με |

| tpwis             | Input Strobe Pulse Width                                             | 200  |      | 200  |                      | 150  |      | 100  |      | ns |

| tiH               | Input Data Hold Time                                                 | 50   |      | 50   |                      | 40   |      | 30   |      | ns |

| tis               | Input Data Setup Time                                                | 20   |      | 20   |                      | 20   |      | 20   |      | ns |

Figure 2: Data Setup and Hold Times (MPU read).

<sup>\*</sup> Port 3 non-latched operation (latch enable - 0)

Figure 4: Port 3 Output Strobe Timing (EF6801 single-chip Mode).

<sup>\*</sup> Access matches Output Strobe Select (OSS = 0, a read. OSS = 1, a write).

Notes: 1, 10 k Pullup resistor required for Port 2 to reach 0.7 Vcc.

Figure 5: Port 3 Latch Timing (EF6801 single-chip mode).

SGS-THOMSON

<sup>2.</sup> Not applicable to P21.

<sup>3.</sup> Port 4 cannot be pulled above Vcc.

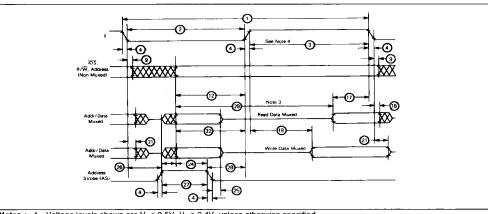

BUS TIMING (see notes 1 and 2)

| Ident. | Symbol Parameter                |                                         |      | 801<br>803 | EF68 |      | EF68  | 3A01<br>3A03 | EF68B01<br>EF68B03 |      | Unit |

|--------|---------------------------------|-----------------------------------------|------|------------|------|------|-------|--------------|--------------------|------|------|

| Number |                                 |                                         | Min. | Max.       | Min. | Max. | Min.  | Max.         | Min.               | Max. |      |

| 1      | t <sub>cyc</sub>                | Cycle Time                              | 1.0  | 2.0        | 0.8  | 2.0  | 0.667 | 2.0          | 0.5                | 2.0  | μs   |

| 2      | PW <sub>EL</sub>                | Pulse Width, E Low                      | 430  | 1000       | 360  | 1000 | 300   | 1000         | 210                | 1000 | ns   |

| 3      | PWEH                            | Pulse Width, E High                     | 450  | 1000       | 360  | 1000 | 300   | 1000         | 220                | 1000 | ns   |

| 4      | t <sub>r</sub> , t <sub>f</sub> | Clock Rise and Fall Time                |      | 25         |      | 25   |       | 25           |                    | 20   | ns   |

| 9      | t <sub>AH</sub>                 | Address Hold Time                       | 20   |            | 20   |      | 20    |              | 10                 |      | ns   |

| 12     | t <sub>AV</sub>                 | Non-muxed Address Valid<br>Time to E*   | 200  |            | 150  |      | 115   |              | 70                 |      | ns   |

| 17     | t <sub>DSR</sub>                | Read Data Setup Time                    | 80   |            | 70   |      | 60    |              | 40                 |      | ns   |

| 18     | t <sub>DHR</sub>                | Read Data Hold Time                     | 10   |            | 10   |      | 10    |              | 10                 |      | ns   |

| 19     | t <sub>DDW</sub>                | Write Data Delay Time                   |      | 225        |      | 200  |       | 170          |                    | 120  | ns   |

| 21     | t <sub>DHW</sub>                | Write Data Hold Time                    | 20   |            | 20   |      | 20    |              | 10                 |      | ns   |

| 22     | t <sub>AVM</sub>                | Muxed Address Valid<br>Time to E Rise*  | 200  |            | 150  |      | 115   |              | 80                 |      | ns   |

| 24     | tası                            | Muxed Address Valid<br>Time to AS Fall* | 60   |            | 50   |      | 40    |              | 20                 |      | ns   |

| 25     | tahl                            | Muxed Address Hold Time                 | 20   |            | 20   |      | 20    |              | 10                 |      | ns   |

| 26     | tasp                            | Delay Time, E to AS Rise*               | 90** |            | 70** |      | 60**  |              | 45**               |      | ns   |

| 27     | PWASH                           | Pulse Width, AS High*                   | 220  |            | 170  |      | 140   |              | 110                |      | ns   |

| 28     | tased                           | Delay Time, AS to E Rise*               | 90   |            | 70   |      | 60    |              | 45                 |      | ns   |

| 29     | tACC                            | Usable Access Time*                     | 595  |            | 465  |      | 380   |              | 270                |      | ns   |

<sup>\*</sup> At specified cycle time.

Figure 6: Bus Timing.

**Notes**: 1. Voltage levels shown are  $V_L \le 0.5V$ ,  $V_H \ge 2.4V$ , unless otherwise specified.

6/49

SGS-THOMSON MICROELECTRONICS

<sup>\*</sup> t<sub>ASD</sub> parameters listed assume external TTL clock drive with 50% ± 5% duty cycle. Devices driven by an external TTL clock with 50% ± 1% duty cycle or which use a crystal have the following t<sub>ASD</sub> specifications: 100ns min. (1.0MHz devices), 80ns min. (1.25MHz devices), 65ns min. (1.5MHz devices), 50ns min. (2.0MHz devices).

<sup>2.</sup> Measurement points shown are 0.8V and 2.0V, unless otherwise specified.

<sup>3.</sup> Usable access time is computed by 12 + 3 - 17 + 4.

<sup>4.</sup> Memory devices should be enabled only during E high to avoid Port 3 bus contention.

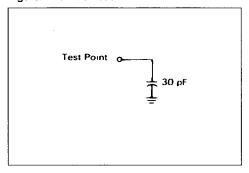

Figure 7: CMOS Load.

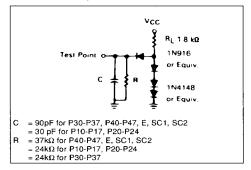

Figure 8: Timing Test Load Ports 1, 2, 3, 4.

#### INTRODUCTION

The EF6801 is an 8-bit monolithic microcomputer which can be configured to function in a wide variety of applications. The facility which provides this extraordinary flexibility is its ability to be hardware programmed into eight different operating modes. The operating mode controls the configuration of 18 of the 40 MCU pins, available on-chip resources, memory map, location (internal or external) of interrupt vectors, and type of external bus. The configuration of the remaining 22 pins is not dependent on the operating mode.

Twenty-nine pins are organized as three 8-bit ports and one 5-bit port. Each port consists of at least a Data Register and a write-only Data Direction Register. The Data Direction Register is used to define whether corresponding bits in the Data Register are configured as an input (clear) or output (set).

The term "port", by itself, refers to all of the hardware associated with the port. When the port is used as a "data port" or "I/O port", it is controlled by the port Data Direction Register and the programmer has direct access to the port pins using the port Data Register. Port pins are labled as Pij where i identifies one of four ports and j indicates the particular bit.

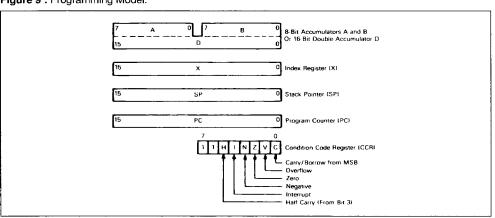

The Microprocessor Unit (MPU) is an enhanced EF6800 MPU with additional capabilities and greater throughput. It is upward source and object code compatible with the EF6800. The programming model is depicted in figure 9, where Accumulator D is a concatenation of Accumulators A and B. A list of new operations added to the 6800 instruction set are shown in table 1.

The EF6803 can be considered an EF6801 that operates in Modes 2 and 3 only.

Figure 9: Programming Model.

SGS-THOMSON MICROELECTRONICS

7/49

### **OPERATING MODES**

The EF6801 provides eight different operating modes (modes 0 through 7), the EF6803 provides two operating modes (modes 2 and 3). The operating modes are hardware selectable and determine the device memory map, the configuration of Port 3, Port 4, SC1, SC2, and the physical location of the interrupt vectors.

#### FUNDAMENTAL MODES

The eight operating modes can be grouped into three fundamental modes which refer to the type of bus it supports: Single Chip, Expanded Non-Multiplexed, and Expanded Multiplexed. Single-Chip modes include 4 and 7, Expanded Non-Multiplexed

is Mode 5 and the remaining five are Expanded Multiplexed modes. Table 2 summarizes the characteristics of the operating modes.

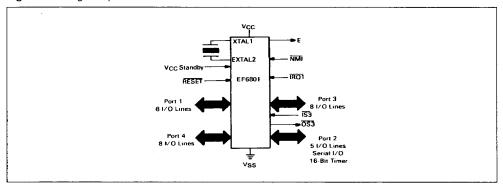

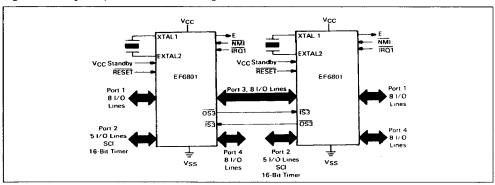

EF6801 SINGLE-CHIP MODES (4, 7). In the Single-Chip Mode, the four MCU ports are configured as parallel input/output data ports, as shown in figure 10. The MCU functions as a monolithic microcomputer in these two modes without external address or data buses. A maximum of 29 I/O lines and two Port 3 control lines are provided. Peripherals or another MCU can be interfaced to Port 3 in a loosely coupled dual processor configuration, as shown in figure 11.

Table 1: New Instructions.

| Instruction  | <b>Description</b>                                                                                                               |

|--------------|----------------------------------------------------------------------------------------------------------------------------------|

| ABX          | Unsigned addition of accumulator B to index register.                                                                            |

| ADDD         | Adds (without carry) the double accumulator to memory and leaves the sum in the double accumulator.                              |

| ASLD or LSLD | Shifts the double accumulator left (towards MSB) one bit; the LSB is cleared and the MSB is shifted into the C-bit.              |

| BHS          | Branch if higher or same; unsigned conditional branch (same as BCC).                                                             |

| BLO          | Branch if lower; unsigned conditional branch (same as BCS).                                                                      |

| BRN          | Branch never.                                                                                                                    |

| JSR          | Additional addressing mode direct.                                                                                               |

| LDD          | Loads double accumulator from memory.                                                                                            |

| LSL          | Shifts memory or accumulator left (towards MSB) one bit; the LSB is cleared and the MSB is shifted into the C-bit (same as ASL). |

| LSRD         | Shifts the double accumulator right (towards LSB) one bit; the MSB is cleared and the LSB is shifted into the C-bit.             |

| MUL          | Unsigned multiply; multiplies the two accumulators and leaves the product in the double accumulator.                             |

| PSHX         | Pushes the index register to stack.                                                                                              |

| PULX         | Pulls the index register from stack.                                                                                             |

| STD          | Stores the double accumulator to memory.                                                                                         |

| SUBD         | Substracts memory from the double accoumulator and leaves the difference in the double accumulator.                              |

| CPX          | Internal processing modified to permit its use with any conditional branch instruction.                                          |

In Single-Chip Test Mode (4), the RAM responds to \$XX80 through \$XXFF and the ROM is removed from the internal address map. A test program must first be loaded into the RAM using modes 0, 1, 2, or 6. If the MCU is Reset and then programmed into Mode 4, execution will begin at \$XXFE: XXFF. Mode 5 can be irreversibly entered from Mode 4 without asserting RESET by setting bit 5 of the Port 2 Data Register. This mode is used primarily to test Ports 3 and 4 in the Single-Chip and Non-Multiplexed Modes.

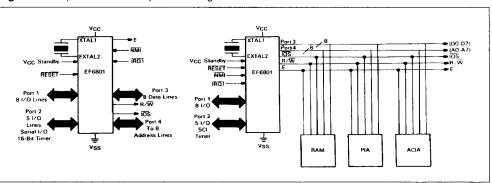

EF6801 EXPANDED NON-MULTIPLEXED MODE (5). A modest amount of external memory space is

provided in the Expanded Non-Multiplexed Mode while significant on-chip resources are retained. Port 3 functions as an 8-bit bidirectional data bus and Port 4 is configured initially as an input data port. Any combination of the eight least-significant address lines may be obtained by writing to the Port 4 Data Direction Register. Stated alternatively, any combination of A0 to A7 may be provided while retaining the remainder as input data lines. Internal pullup resistors pull the Port 4 lines high until the port is configured.

Figure 12 illustrates a typical system configuration in the Expanded Non-Multiplexed Mode. The MCU

interfaces directly with 6800 family parts and can access 256 bytes of external address space at \$100 through \$1FF. IOS provides an address decode of

external memory (\$100-\$1FF) and can be used as a memory page select or chip select line.

Table 2: Summary of EF6801/03 Operating Modes.

#### Common to all Modes:

Reserved Register Area

Port 1

Port 2

Programmable Timer

Serial Communications Interface

# Single-chip Mode 7:

128 Bytes of RAM, 2048 Bytes of ROM

Port 3 is a parallel I/O port with two control lines.

Port 4 is a parallel I/O port.

SC1 is input strobe 3 (IS3).

SC2 is output strobe (OS3).

# Expanded Non-multiplexed Mode 5:

128 Bytes of RAM, 2048 Bytes of ROM

256 Bytes of External Memory Space

Port 3 is an 8-bit data bus.

Port 4 is an input port/address bus.

SC1 is input/output select (IOS).

SC2 is read/write (R/W).

# Expanded Multiplexed Modes 1, 2, 3, 6\*:

Four memory space options (64K address space).

- (1) No Internal RAM or ROM (mode 3)

- (2) Internal RAM, no ROM (mode 2)

- (3) Internal RAM and ROM (mode 1)

- (4) Internal RAM, ROM with Partial Address Bus (mode 6)

Port 3 is multiplexed address/data bus.

Port 4 is an address bus (inputs/address in mode 6).

SC1 is address strobe (AS).

SC2 is read/write (R/W).

#### Test Modes 0 and 4:

Expanded multiplexed test mode 0.

May be used to test RAM and ROM.

Single chip and non-multiplexed test mode 4.

- (1) May be changed to mode 5 without going through reset.

- (2) May be used to test ports 3 and 4 as I/O ports.

<sup>\*</sup> The EF6803 operates only in modes 2 and 3

Figure 10 : Single-chip Mode.

Figure 11: Single-chip Dual Processor Configuration.

Figure 12: Expanded Non-multiplexed Configuration.

EXPANDED-MULTIPLEXED MODES (0, 1, 2, 3, 6). A 64K byte memory space is provided in the expanded multiplexed modes. In each of the expanded multiplexed modes Port 3 functions as a time multiplexed address/data bus with address valid on the negative edge of Address Strobe (AS), and data valid while E is high. In Modes 0 to 3, Port 4 provides address lines A8 to A15. In Mode 6, however, Port 4 initially is configured at RESET as an input data port. The port 4 Data Direction Register can then be changed to provide any combination of address lines, A8 to A15. Stated alternatively, any subset of A8 to A15 can be provided while retaining the remaining port 4 lines as input data lines. Internal pullup resistors pull the Port 4 lines high until software configures the port.

In Mode 0, the Reset vector is external for the first two E-cycles after the positive edge of RESET, and internal thereafter. In addition, the internal and external data buses are connected so there must be no memory map overlap in order to avoid potential bus conflicts. Mode 0 is used primarily to verify the ROM pattern and monitor the internal data bus with the automated test equipment.

Only the EF6801 can operate in each of the expanded multiplexed modes. The EF6803 operates only in Modes 2 and 3.

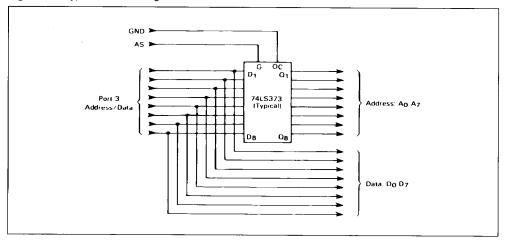

Figure 13 depicts a typical configuration for the Expanded-Multiplexed Modes. Address Strobe can be used to control a transparent D-type latch to capture addresses A0-A7, as shown in figure 14. This allows Port 3 to function as a Data Bus when E is high.

#### PROGRAMMING THE MODE

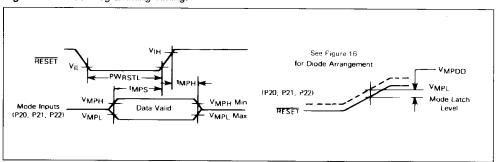

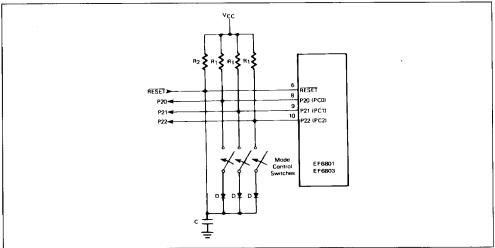

The operating mode is determined at RESET by the levels asserted on P22, P21, and P20. These levels are latched into PC2, PC1, and PC0 of the program control register on the positive edge of RESET. The operating mode may be read from the Port 2 Data Register as shown below, and programming levels and timing must be met as shown in figure 15. A brief outline of the operating modes is shown in table 3.

| PORT 2 DATA REGISTER 7 6 5 4 3 2 1 0 |     |     |     |     |     |     |     |        |

|--------------------------------------|-----|-----|-----|-----|-----|-----|-----|--------|

| PC2                                  | PC1 | PC0 | P24 | P23 | P22 | P21 | P20 | \$0003 |

Circuitry to provide the programming levels is dependent primarily on the normal system usage of the three pins. If configured as outputs, the circuit shown in figure 16 may be used; otherwise, threestate buffers can be used to provide isolation while programming the mode.

Table 3: Mode Selection Summary.

| Mode* | P22<br>PC2 | P21<br>PC1 | P20<br>PC0 | ROM               | RAM   | Interrupt<br>Vectors | Bus Mode    | Operating Mode                 |

|-------|------------|------------|------------|-------------------|-------|----------------------|-------------|--------------------------------|

| 7     | Н          | Н          | Н          | I                 | ı     | 1                    | ı           | Single Chip                    |

| 6     | Н          | Н          | L          | T                 | 1     | I                    | MUX (5, 6)  | Multiplexed/partial Decode     |

| 5     | Н          | L          | н          | i                 | t     | ı                    | NMUX (5, 6) | Non-multiplexed/partial Decode |

| 4     | Н          | L          | L          | I <sup>{2</sup> ) | J (1) | 1                    | ı           | Single Chip Test               |

| 3     | L          | н          | Н          | Е                 | E     | E                    | MUX (4)     | Multiplexed/no RAM or ROM      |

| 2     | L          | Н          | L          | Е                 | ı     | E                    | MUX (4)     | Multiplexed/RAM                |

| 1     | L          | L          | Н          | !                 | ı     | E                    | MUX (4)     | Multiplexed/RAM & ROM          |

| 0     | L          | L          | L          | ı                 | 1     | 1 (3)                | MUX (4)     | Multiplexed Test               |

Legend:

I - Internal

E - External

MUX - Multiplexed NMUX - Non-Multiplexed

L - Logic "0" H - Logic "1" Notes: (1) Internal RAM is addressed at \$XX80 (2) Internal ROM is disabled

(3) RESET vector is external for 2 cycles after RESET goes high

(4) Addresses associated with Ports 3 and 4 are considered external in Modes 0, 1, 2, and 3

(5) Addresses associated with Port 3 are considered external in Modes 5 and 6

(6) Port 4 default is user data input, address output is optional by writing to Port 4 Data Direction Register

<sup>\*</sup> The EF6803 operates only in Modes 2 and 3

Figure 13: Expanded Multiplexed Configuration.

Note: To avoid data bus (Port 3) contention in the expanded multiplexed modes, memory devices should be enabled only during E high time.

Figure 14: Typical Latch Arrangement.

Figure 15: Mode Programming Timing.

# MODE PROGRAMMING (refer to figure 15)

| Symbol           | Parameter                                                                           | Min.     | Max. | Unit     |

|------------------|-------------------------------------------------------------------------------------|----------|------|----------|

| V <sub>MPL</sub> | Mode Programming Input Voltage Low*                                                 |          | 1.8  | V        |

| V <sub>MPH</sub> | Mode Programming Input Voltage High                                                 | 4.0      |      | V        |

| $V_{MPDD}$       | Mode Programming Diode Differential (if diodes are used)                            | 0.6      |      | V        |

| $PW_{RSTL}$      | RESET Low Pulse Width                                                               | 3.0      |      | E-Cycles |

| t <sub>MPS</sub> | Mode Programming Setup Time                                                         | 2.0      |      | E-Cycles |

| t <sub>MPH</sub> | Mode Programming Hold Time<br><u>RESET</u> Rise Time ≥ 1μs<br>RESET Rise Time < 1μs | 0<br>100 |      | ns       |

<sup>\*</sup> For  $T_A = -40$  \*C to + 105 °C,  $V_{MPL} = 1.7 V$ .

Figure 16: Typical Mode Programming Circuit.

Notes: 1. Mode 7 as shown

2. R<sub>2</sub>.C = Reset time constant

R<sub>1</sub> = 10k (typical)

4. D = 1N914, 1N4001 (typical)

5. Diode V<sub>1</sub> should not exceed V<sub>MPDD</sub> min

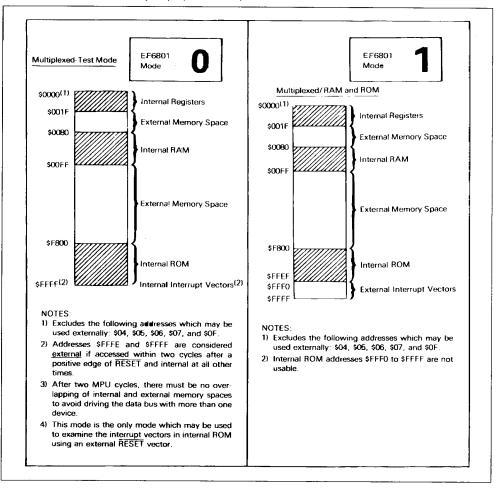

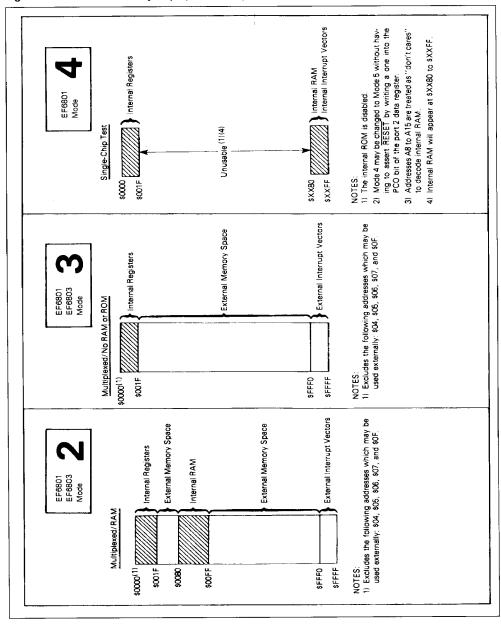

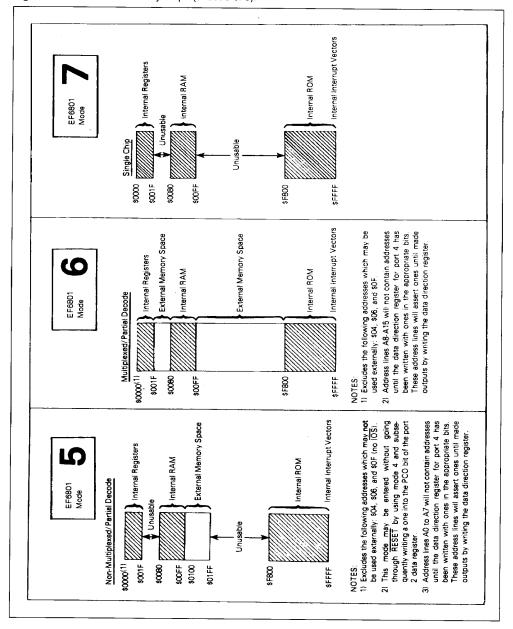

# MEMORY MAPS

The 6801 Family can provide up to 64K byte address space depending on the operating mode. A memory map for each operating mode is shown in figure 17.

The first 32 locations of each map are reserved for the internal register area, as shown in table 4, with exceptions as indicated.

Figure 17: EF6801/03 Memory Maps (sheet 1 of 3).

Figure 17: EF6801/03 Memory Maps (sheet 2 of 3).

16/49

SGS-THOMSON MICROELECTRONICS

Figure 17: EF6801/03 Memory Maps (sheet 3 of 3).

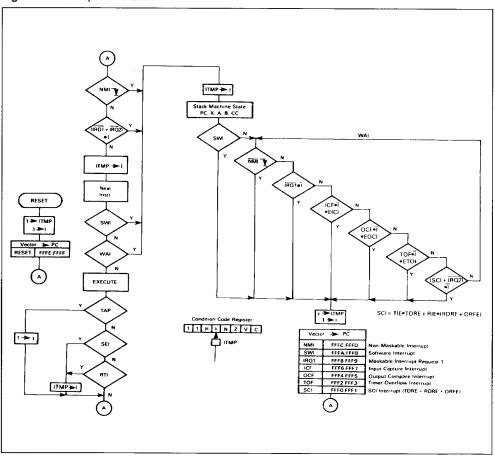

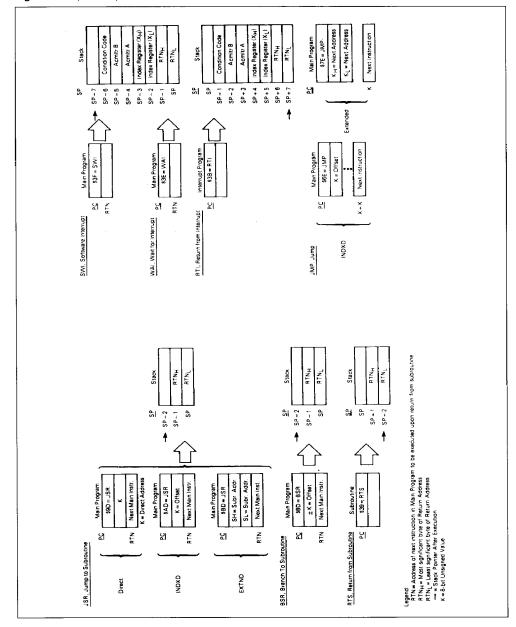

# EF6801/03 INTERRUPTS

The 6801 Family supports two types of interrupt requests: maskable and non-maskable. A Non-Maskable Interrupt (NMI) is always recognized and acted upon at the completion of the current instruction. Maskable interrupts are controlled by the Condition Code Register I-bit and by individual enable bits. The I-bit controls all maskable interrupts. Of the maskable interrupts, there are two types: IRQ1 and IRQ2. The Programmable Timer and Serial Communications Interface use an internal IRQ2 interrupt line, as shown in figure 1. External devices (and IS3) use IRQ1. An IRQ1 interrupt is serviced before IRQ2 if both are pending.

All IRQ2 interrupts use hardware prioritized vectors. The single SCI interrupt and three timer interrupts

#### **FUNCTIONAL PIN DESCRIPTIONS**

Vcc AND Vss

$V_{CC}$  and  $V_{SS}$  provide power to a large portion of the MCU. The power supply should provide + 5 volts ( $\pm$  5%) to  $V_{CC}$ , and  $V_{SS}$  should be tied to ground. Total power dissipation (including  $V_{CC}$  Standby), will not exceed  $P_D$  milliwatts.

**VCC STANDBY**

V<sub>CC</sub> Standby provides power to the standby portion (\$80 through \$BF) of the RAM and the STBY PWR and RAME bits of the RAM Control Register. Voltage requirements depend on whether the device is in a powerup or powerdown state. In the powerup state, the power supply should provide + 5 volts (± 5%) and must reach VSB volts before RESET reaches 4.0 volts. During powerdown, Vcc Standby must remain above VSBB (min) to sustain the standby RAM and STBY PWR bit. While in powerdown operation, the standby current will not exceed ISBB. It is typical to power both Vcc and Vcc Standby from the same source during normal operation. A diode must be used between them to prevent supplying power to Vcc during powerdown operation. Vcc Standby should be tied to ground in Mode 3.

are serviced in a prioritized order and each is vectored to a separate location. All interrupt vector locations are shown in table 5.

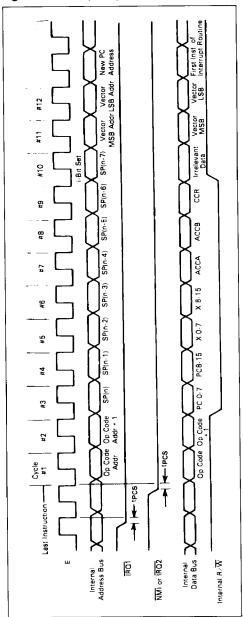

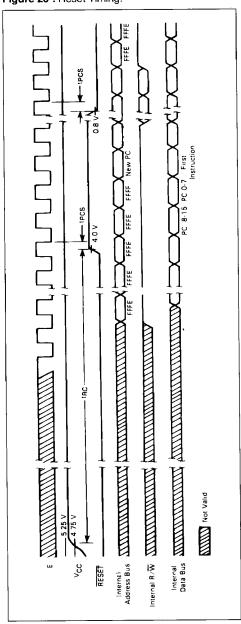

The Interrupt flowchart is depicted in figure 18 and is common to every interrupt excluding reset. During interrupt servicing the Program Counter, Index Register, A Accumulator, B Accumulator, and Condition Code Register are pushed to the stack. The I-bit is set to inhibit maskable interrupts and a vector is fetched corresponding to the current highest priority interrupt. The vector is transferred to the Program Counter and instruction execution is resumed. Interrupt and RESET timing are illustrated in figures 19 and 20.

Table 4: Internal Register Area.

| Register                                                            | Address     |

|---------------------------------------------------------------------|-------------|

| Port 1 Data Direction Register*** Port 2 Data Direction Register*** | 00<br>01    |

| Port 1 Data Register                                                | 02          |

| Port 2 Data Register                                                | 03          |

| Port 3 Data Direction Register***                                   | 04*         |

| Port 4 Data Direction Register***                                   | 05**        |

| Port 3 Data Register                                                | 06*<br>07** |

| Port 4 Data Register                                                | <del></del> |

| Timer Control and Status Register                                   | 08          |

| Counter (high byte)                                                 | 09<br>0A    |

| Counter (low byte) Output Compare Register (high byte)              | 0B          |

| Output Compare Register (low byte)                                  | OC.         |

| Input Capture Register (high byte)                                  | OD          |

| Input Capture Register (low byte)                                   | 0E          |

| Port 3 Control and Status Register                                  | 0F*         |

| Rate and Mode Control Register                                      | 10          |

| Transmit/receive Control and Status Register                        | 11          |

| Receive Data Register                                               | 12          |

| Transmit Data Register                                              | 13          |

| RAM Control Register                                                | 14          |

| Reserved                                                            | 15-1F       |

<sup>\*</sup> External addresses in Modes 0, 1, 2, 3, 5, 6; cannot be accessed in Mode 5 (No iOS)

<sup>&</sup>quot; External addresses in Modes 0, 1, 2, 3

<sup>\*\*\* 1 =</sup> Output, 0 = Input

Table 5: MCU Interrupt Vector Locations.

| MSB    | LSB  | Interrupt                 |  |  |  |

|--------|------|---------------------------|--|--|--|

| FFFE   | FFFF | RESET                     |  |  |  |

| FFFC   | FFFD | NMI                       |  |  |  |

| FFFA   | FFFB | Software Interrupt (SWI)  |  |  |  |

| FFF8   | FFF9 | IRQ1 (or IS3)             |  |  |  |

| FFF6   | FFF7 | ICF (input capture)*      |  |  |  |

| FFF4   | FFF5 | OCF (output compare)*     |  |  |  |

| FFF2   | FFF3 | TOF (timer overflow)*     |  |  |  |

| , FFF0 | FFF1 | SCI (RDRF + ORFE + TDRE)* |  |  |  |

<sup>\*</sup> IRQ2 Interrupt

Figure 18: Interrupt Flowchart.

Figure 19: Interrupt Sequence.

Figure 20 : Reset Timing.

20/49

SGS-THOMSON MICROELECTRONICS

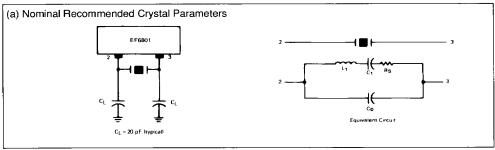

#### XTAL1 AND EXTAL2

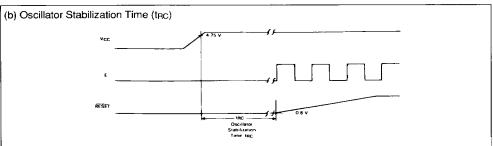

These two input pins interface either a crystal or TTL compatible clock to the MCU internal clock generator. Divide-by-four circuitry is included which allows use of the inexpensive 3.58MHz or 4.4336MHz Color Burst TV crystals. A 20pF capacitor should be tied from each crystal pin to ground to ensure reliable startup and operation. Alternatively, EXTAL2 may be driven by an external TTL compatible clock at 4f<sub>0</sub> with a duty cycle of 50% (± 5%) with XTAL1 connected to ground.

The internal oscillator is designed to interface with an AT-cut quartz crystal resonator operated in parallel resonance mode in the frequency range specified for f<sub>XTAL</sub>. The crystal should be mounted as close as possible to the input pins to minimize output distortion and startup stabilization time.\* The MCU is compatible with most commercially available crystals. Nominal crystal parameters are shown in figure 21.

# RESET

This input is used to reset the internal state of the device and provide an orderly startup procedure. During powerup, RESET must be held below 0.8 volts: (1) at least the after Vcc reaches 4.75 volts in order to provide sufficient time for the clock generator to stabilize, and (2) until Vcc Standby reaches 4.75 volts. RESET must be held low at least three E-cycles if asserted during powerup operation.

# E (ENABLE)

This is an output clock used primarily for bus synchronization. It is TTL compatible and is the slightly skewed divide-by-four result of the device input clock frequency. It will drive one Schottky TTL load and 90pF, and all data given in cycles is referenced to this clock unless otherwise noted.

# NMI (NON-MASKABLE INTERRUPT)

An  $\overline{\text{NMI}}$  negative edge requests an MCU interrupt sequence, but the current instruction will be completed before it responds to the request. The MCU will then begin an interrupt sequence. Finally, a vector is fetched from \$FFFC and \$FFFD, transferred to the Program Counter and instruction execution is resumed. NMI typically requires a  $3.3\text{k}\Omega$  (nominal) resistor to VCc. There is no internal NMI pullup resistor. NMI must be held low for at least one E-cycle to be recognized under all conditions.

### IRQ1 (MASKABLE INTERRUPT REQUEST 1)

IRQ1 is a level-sensitive input which can be used to request an interrupt sequence. The MPU will com-

plete the current instruction before it responds to the request. If the interrupt mask bit (I-bit) in the Condition Code Register is clear, the MCU will begin an interrupt sequence. A vector is fetched from \$FFF8 and \$FFF9, transferred to the Program Counter, and instruction execution is resumed.

IRQ1 typically requires an external 3.3k $\Omega$  (nominal) resistor to V<sub>CC</sub> for wire-OR applications. IRQ1 has no internal pullup resistor.

# SC1 AND SC2 (STROBE CONTROL 1 AND 2)

The function of SC1 and SC2 depends on the operating mode. SC1 is configured as an output in all modes except single chip mode, whereas SC2 is always an output. SC1 and SC2 can drive one Schottky load and 90pF.

SC1 AND SC2 IN SINGLE-CHIP MODE. In Single-Chip Mode, SC1 and SC2 are configured as an input and output, respectively, and both <u>function</u> as Port 3 control lines. SC1 functions as IS3 and can be used to indicate that Port 3 input data is ready or output data has been accepted. Three options associated with IS3 are controlled by Port 3 Control and Status Register and are discussed in the Port 3 description. If unused, IS3 can remain unconnected.

SC2 is configured as  $\overline{OS3}$  and can be used to strobe output data or acknowledge input data. It is controlled by Output Strobe Select (OSS) in the Port 3 Control and Status Register. The strobe is generated by a read (OSS = 0) or write (OSS = 1) to the Port 3 Data Register. OS3 timing is shown in figure 4.

SC1 AND SC2 IN EXPANDED NON-MULTI-PLEXED MODE. In the Expanded Non-Multiplexed Mode, both SC1 and SC2 are configured as outputs. SC1 functions as Input/Output Select (IOS) and is asserted only when \$0100 through \$01FF is sensed on the internal address bus.

SC2 is configured as Read/Write and is used to control the direction of data bus transfers. An MPU read is enabled when Read/Write and E are high.

SC1 AND SC2 IN EXPANDED MULTIPLEXED MODE. In the Expanded Multiplexed Modes, both SC1 and SC2 are configured as outputs. SC1 functions as Address Strobe and can be used to demultiplex the eight least significant addresses and the data bus. A latch controlled by Address Strobe captures address on the negative edge, as shown in figure 14.

SC2 is configured as Read/Write and is used to control the direction of data bus transfers. An MPU read is enabled when Read/Write and E are high.

## P10-P17 (PORT 1)

Port 1 is a mode independent 8-bit I/O port with each line an input or output as defined by the Port 1 Data Direction Register. The TTL compatible three-state output buffers can drive one Schottky TTL load and 30pF, Darlington transistors, or CMOS devices using external pullup resistors. It is configured as a data input port by RESET. Unused lines can remain unconnected.

# P20-P24 (PORT 2)

Port 2 is a mode-independent, 5-bit, multipurpose I/O port. The voltage levels <u>present</u> on P20, P21, and P22 on the rising edge of RESET determine the operating mode of the MCU. The entire port is then configured as a data input port. The Port 2 lines can be selectively configured as data output lines by setting the appropriate bits in the Port 2 Data Direction

Register. The Port 2 Data Register is used to move data through the port. However, if P21 is configured as an output, it will be tied to the timer Output Compare function and cannot be used to provide output from the Port 2 Data Register.

Port 2 can also be used to provide an interface for the Serial Communications Interface and the timer Input Edge function. These configurations are described in the Programmable Timer and Serial Communications Interface (SCI) section.

The Port 2 three-state, TTL-compatible output buffers are capable of driving one Schottky TTL load and 30pF, or CMOS devices using external pullup resistors.

|     | ,   | PORT2 | DATA | REG | ISTER |     |            |

|-----|-----|-------|------|-----|-------|-----|------------|

| 7   | 6   | 5     | 4    | 3   | 2     | 1   | 0          |

| PC2 | PC1 | PC0   | P24  | P23 | P22   | P21 | P20 \$0003 |

Figure 21: 6801 Family Oscillator Characteristics.

# Nominal Crystal Parameters\*

|    | 3.58MHz | 4.00MHz | 5.0MHz      | 6.0MHz      | 8.0MHz      |

|----|---------|---------|-------------|-------------|-------------|

| RS | 60Ω     | 50Ω     | 30-50Ω      | 30-50Ω      | 20-40Ω      |

| CO | 3.5pF   | 6.5pF   | 4-6pF       | 4-6pF       | 4-6pF       |

| C1 | 0.015pF | 0.025pF | 0.01-0.02pF | 0.01-0.02pF | 0.01-0.02pF |

| Q  | > 40K   | > 30K   | > 20K       | > 20K       | > 20K       |

Note: These are representative AT-cut crystal parameters only. Crystals of other types of cut may also be used.

22/49

SGS-THOMSON MICROELECTRONICS

#### P30-P37 (PORT 3)

Port 3 can be configured as an I/O port, a bidirectional 8-bit data bus, or a multiplexed address/data bus depending on the operating mode. The TTL compatible three-state output buffers can drive one Schottky TTL load and 90pF. Unused lines can remain unconnected.

PORT 3 IN SINGLE-CHIP MODE. Port 3 is an 8-bit I/O port in the Single-Chip Mode, with each line configured by the Port 3 Data <u>Direction</u> Register. There are also two lines, IS3 and OS3, which can be used to control Port 3 data transfers.

Three Port 3 options are controlled by the Port 3 Control and Status Register and are available only in Single-Chip Mode: (1) Port 3 input data can be latched using IS3 as a control signal, (2) OS3 can be generated by either an MPU read or write to the Port 3 Data Register, and (3) an IRQ1 interrupt can be enabled by an IS3 negative edge. Port 3 latch timing is shown in figure 5.

# PORT 3 CONTROL AND STATUS REGISTER

| <u></u> |                       |   | NI. |        |   |   |   | _      |

|---------|-----------------------|---|-----|--------|---|---|---|--------|

| IS3     | IS3<br>IRQ1<br>Enable | Х | oss | Enable | х | × | x | \$000F |

| 7       | 6                     | 5 | 4   | 3      | 2 | 1 | 0 |        |

Bit 0-2 Not used.

Bit 3

LATCH ENABLE. This bit controls the input latch for Port 3. If set, input data is latched by an IS3 negative edge. The latch is transparent after a read of the Port 3 Data Register. LATCH ENABLE is cleared during reset.

OSS (Output Strobe Select). This bit determines whether OS3 will be generated by a read or write of the Port 3 Data Register. When clear, the strobe is generated by a read; when set, it is generated by a write. OSS is cleared during reset.

Bit 5 Not used.

Bit 4

Bit 6

IS3 IRQ1 ENABLE. When set, an IRQ1 interrupt will be enabled whenever IS3 FLAG is set; when clear, the interrupt is inhibited. This bit is cleared during reset.

Bit 7

IS3 FLAG. This read-only status bit is set by an IS3 negative edge. It is cleared by a read of the Port 3 Control and Status Register (with IS3 FLAG set) followed by a read or write to the Port 3 Data Register or during reset.

PORT 3 IN EXPANDED NON-MULTIPLEXED MODE. Port 3 is configured as a bidirectional data bus (D7-D0) in the Expanded Non-Multiplexed Mode. The direction of data transfers is controlled by Read/Write (SC2). Data is clocked by E (Enable).

PORT 3 IN EXPANDED MULTIPLEXED MODE. Port 3 is configured as a time multiplexed address (A0-A7) and data bus (D7-D0) in the Expanded Multiplexed Modes, where Address Strobe (AS) can be used to demultiplex the two buses. Port 3 is held in a high impedance state between valid address and data to prevent bus conflicts.

# P40-P47 (PORT 4)

Port 4 is configured as an 8-bit I/O port, as address outputs, or as data inputs depending on the operating mode. Port 4 can drive one Schottky TTL load and 90pF and is the only port with internal pullup resistors. Unused lines can remain unconnected.

PORT 4 IN SINGLE-CHIP MODE. In Single-Chip Mode, Port 4 functions as an 8-bit I/O port with each line configured by the Port 4 Data Direction Register. Internal pullup resistors allow the port to directly interface with CMOS at 5 volt levels. External pullup resistors to more than 5 volts, however, cannot be used.

PORT 4 IN EXPANDED NON-MULTIPLEXED MODE. Port 4 is configured from reset as an 8-bit input port, where the Port 4 Data Direction Register can be written to provide any or all of eight address lines, A0 to A7. Internal pullup resistors pull the lines high until the Port 4 Data Direction Register is configured.

PORT 4 IN EXPANDED MULTIPLEXED MODE. In all Expanded Multiplexed modes except Mode 6, Port 4 functions as half of the address bus and provides A8 to A15. In Mode 6, the port is configured from reset as an 8-bit parallel input port, where the Port 4 Data Direction Register can be written to provide any or all of upper address lines A8 to A15. Internal pullup resistors pull the lines high until the Port 4 Data Direction Register is configured, where bit 0 controls A8.

### RESIDENT MEMORY

The EF6801 provides 2048 bytes of on-board ROM and 128 bytes of on-board RAM.

One half of the RAM is powered through the  $V_{CC}$  standby pin and is maintainable during  $V_{CC}$  powerdown. This standby portion of the RAM consists of 64 bytes located from \$80 through \$BF.

Power must be supplied to V<sub>CC</sub> standby if the internal RAM is to be used regardless of whether standby power operation is anticipated.

The RAM is controlled by the RAM Control Register.

# RAM CONTROL REGISTER (\$14)

The RAM Control Register includes two bits which can be used to control RAM accesses and determine the adequacy of the standby power source during powerdown operation. It is intended that RAME be cleared and STBY PWR be set as part of a powerdown procedure.

|            |      | RAM C | ONTR | OL REC | SISTER | ł |   |

|------------|------|-------|------|--------|--------|---|---|

| 7          | 6    | 5     | 4    | 3      | 2      | 1 | 0 |

| STY<br>PWR | RAME | Х     | Х    | х      | Х      | X | Х |

Bit 0-5

Not used

Bit 6 RAME

RAM Enable. This read/write bit can be used to remove the en-

Figure 22: Block Diagram of Programmable Timer.

tire RAM from the internal memory map. RAME is set (enabled) during reset provided standby power is available on the positive edge of RESET. If RAME is clear, any access to a RAM address is external. If RAME is set and not in mode 3, the RAM is included in the internal map.

Bit 7 STBY PWR

Standby Power. This bit is a read/write status bit which, when once set, remains set as long as V<sub>CC</sub> standby remains above V<sub>SBB</sub> (minimum). As long as this bit is set following a period of standby operation, the standby power supply has adequately preserved the data in the standby RAM. If this bit is cleared during a period of standby operation, it indicates that V<sub>CC</sub> standby had fallen to a level sufficiently below V<sub>SBB</sub> (minimum) to suspect that data in the standby RAM is not valid. This bit can be set only by software and is not affected during reset.

24/49

SGS-THOMSON MICROELECTRONICS

#### PROGRAMMARI E TIMER

The programmable timer can be used to perform input waveform measurements while independently generating an output waveform. Pulse widths can vary from several microseconds to many seconds. A block diagram of the timer is shown in figure 22.

### COUNTER (\$09:0A)

The key timer element is a 16-bit free-running counter which is incremented by E (enable). It is cleared during reset and is read-only with one exception: a write to the counter (\$09) will preset it to \$FFF8. This feature, intended for testing, can disturb serial operations because the counter provides the SCI internal bit rate clock. TOF is set whenever the counter contains all ones.

# OUTPUT COMPARE REGISTER (\$0B:0C)

The output compare register is a 16-bit read/write register used to control an output waveform or provide an arbitrary timeout flag. It is compared with the free-running counter on each E cycle. When a match occurs, OCF is set and OLVL is clocked to an output level register. If port 2, bit 1, is configured as an output, OLVL will appear at P21 and the output compare register and OLVL can then be changed for the next and OLVL is clocked to an output level register. If Port 2, bit 1, is configured as an output, OLVL will appear at P21 and the Output Compare Register and OLVL can then be changed for the next compare. The function is inhibited for one cycle after a write to its high byte (\$0B) to ensure a valid compare. The Output Compare Register is set to \$FFFF at RESET.

# INPUT CAPTURE REGISTER (\$0D:0E)

The Input Capture Register is a 16-bit read-only register used to store the free-running counter when a "proper" input transition occurs as defined by IEDG. Port 2, bit 0 should be configured as an input, but the edge detect circuit always senses P20 even when configured as an output. An input capture can occur independently of ICF: the register always contains the most current value. Counter transfer is inhibited, however, between accesses of a double byte MPU read. The input pulse width must be at least two E-cycles to ensure an input capture under all conditions.

# TIMER CONTROL AND STATUS REGISTER (\$08)

The Timer Control and Status Register (TCSR) is an 8-bit register of which all bits are readable, while only bits 0-4 can be written. The three most significant bits provide the timer status and indicate if:

- a proper level transition has been detected.

- a match has occured between the free-running counter and the output compare register, and

- the free-running counter has overflowed.

Each of the three events can generate an IRQ2 interrupt and is controlled by an individual enable bit in the TCSR.

# TIMER CONTROL AND STATUS REGISTER (TCSR)

| 7       | 6    | 5   | 4                                   | 3                                       | 2                                          | 1                                                            | 0                                              |                                    |

|---------|------|-----|-------------------------------------|-----------------------------------------|--------------------------------------------|--------------------------------------------------------------|------------------------------------------------|------------------------------------|

| ICF     | OCF  | TOF | EICI                                | EOCI                                    | ETO                                        | IEDG                                                         | OLVL                                           | \$008                              |

| Bit 0   |      |     | cloc<br>ter l<br>pare<br>1 o<br>Reg | cked to<br>by a s<br>e and<br>f the     | the oucces<br>will ap<br>Port              | level.<br>output<br>osful o<br>opear a<br>2 Data<br>It is cl | level<br>utput<br>at P2 <sup>-</sup><br>a Dire | regis-<br>com-<br>if Bit<br>ection |

| Bit 1   |      |     | whi<br>a c<br>Cap                   | ared du<br>ch leve<br>ounter<br>oture F | uring r<br>el trar<br>tran:<br>Regist      |                                                              | will to<br>the                                 | ntrols<br>rigger<br>Input          |

|         |      |     | edg                                 | e<br>G = 1                              |                                            | fer on a                                                     | J                                              |                                    |

| Bit 2   |      |     | terri<br>rupt<br>ove<br>rupt        | upt. W<br>: is e<br>rflow ;             | hen s<br>enable<br>wher                    | imer O<br>et, an I<br>ed foi<br>n clear<br>. It is cl        | IRQ2<br>r a<br>r, the                          | inter-<br>timer<br>inter-          |

| Bit 3 I | EOCI |     | rupt<br>rupt<br>com<br>rupt         | : Whe<br>is en<br>pare                  | n set<br>nable<br>whe                      | Comp<br>t, an II<br>d for<br>n clear<br>. It is cl           | RQ2<br>an o<br>r, the                          | inter-<br>utput<br>inter-          |

| Bit 4 E | EICI |     | Whe<br>ena<br>whe                   | en set<br>bled f<br>en clea             | , an I<br>or an<br>ar, the                 | apture<br>RQ2 i<br>input<br>e inter<br>ired du               | nterru<br>capt<br>rupt                         | upt is<br>ure ;<br>is in-          |

| Bit 5 T | ΓOF  |     | Time when 1's. TCS ing t            | er Ove<br>en the<br>It is c<br>SR (wit  | erflow<br>cour<br>leared<br>th TO<br>unter | Flag.<br>nter co<br>d by re<br>F set)<br>high b              | TOF<br>ontain<br>eading<br>then                | is set<br>is all<br>g the<br>read- |

Bit 6 OCF

Output Compare Flag. OCF is set when the Output Compare Register matches the free-running counter. It is cleared by reading the TCSR (with OCF set) and then writing to the Output Compare Register (\$0B or \$0C), or during reset.

Bit 7 ICE

Input Capture Flag. ICF is set to indicate a proper level transition; it is cleared by reading the TCSR (with ICF set) and then the Input Capture Register High Byte (\$0D), or during reset.

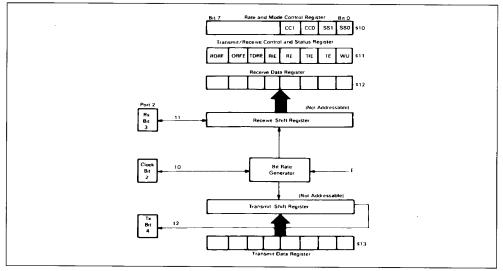

#### SERIAL COMMUNICATIONS INTERFACE (SCI)

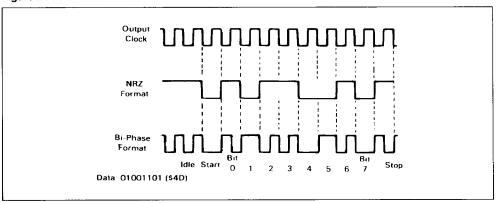

A full-duplex asynchronous Serial Communications Interface (SCI) is provided with two data formats and a variety of rates. The SCI transmitter and receiver are functionally independent, but use the same data format and bit rate. Serial data formats include standard mark/space (NRZ) and Biphase and both provide one start bit, eight data bits, and one stop bit. "Baud" and "bit rate" are used synonymously in the following description.

#### WAKE-UP FEATURE

In a typical serial loop multi-processor configuration, the software protocol will usually identify the addresse(s) at the beginning of the message. In order to permit uninterested MPU's to ignore the remainder of the message, a wake-up feature is included whereby all further SCI receiver flag (and interrupt) processing can be inhibited until its data line goes idle. An SCI receiver is re-enabled by an idle string of ten consecutive 1's or during reset. Software must provide for the required idle string between consecutive messages and prevent it within messages.

# PROGRAMMABLE OPTIONS

The following features of the SCI are programmable:

- format : standard mark/space (NRZ) or Bi-phase

- clock : external or internal bit rate clock

- Baud: one of 4 per E-clock frequency, or external clock (x 8 desired baud)

- wake-up feature : enabled or disabled

- interrupt requests: enabled individually for transmitter and receiver

- clock output : internal bit rate clock enabled or disabled to P22

## SERIAL COMMUNICATIONS REGISTERS

The Serial Communications Interface includes four addressable registers as depicted in figure 23. It is controlled by the Rate and Mode Control Register and the Transmit/Receive Control and Status Register. Data is transmitted and received utilizing write-only Transmit Register and a read-only Receive Register. The shift registers are not accessible to software.

RATE AND MODE CONTROL REGISTER (RMCR) (\$10). The Rate and Mode Control Register controls the SCI bit rate, format, clock source, and under certain conditions, the configuration of P22. The register consists of four write-only bits which are cleared during reset. The two least significant bits control the bit rate of the internal clock and the remaining two bits control the format and clock source.

RATE AND MODE CONTROL REGISTER (RMCR)

| 7      | 6       | 5 | 4                                           | 3                                                                                    | 2                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                   |

|--------|---------|---|---------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Х      | Х       | Х | Х                                           | CC1                                                                                  | CC0                                                         | SS1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SS0 \$0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 010                                                               |

| Bit 1: | : Bit 0 | 1 | The<br>rate<br>clock<br>lect<br>MC<br>lists | whe<br>k. Fo<br>ed wh<br>U inp<br>bit tin                                            | o-bits<br>in us<br>iur ratich are<br>ut free<br>me an       | selecting the test of the test | elect. It the Bane interior of the second of | rnal<br>se-<br>the<br>e 6                                         |