# **Spartan-3E Libraries Guide for Schematic Designs**

**ISE 7.1i**

© 2005 Xilinx, Inc. All Rights Reserved. XILINX, the Xilinx logo, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

NOTICE OF DISCLAIMER: Xilinx is providing this design, code, or information "as is." By providing the design, code, or information as one possible implementation of this feature, application, or standard, Xilinx makes no representation that this implementation is free from any claims of infringement. You are responsible for obtaining any rights you may require for your implementation. Xilinx expressly disclaims any warranty whatsoever with respect to the adequacy of the implementation, including but not limited to any warranties or representations that this implementation is free from claims of infringement and any implied warranties of merchantability or fitness for a particular purpose.

# **About this Guide**

The *Spartan-3E*<sup>TM</sup> *Libraries Guide for Schematic Designs* is part of the ISE documentation collection. A separate version of this guide is also available for users who prefer to work in a hardware description language (HDL) in their circuit design activities. (See *Spartan-3E*<sup>TM</sup> *Libraries Guide for HDL Designs.*)

### **Guide Contents**

This guide contains the following:

- Information about additional resources and conventions used in this guide.

- A general introduction to the Spartan-3E primitives and macros.

- A listing of the Functional Categories into which Spartan-3E design elements are organized.

- Individual sections for each of the applicable design elements.

- Referrals to additional sources of information.

### **Additional Resources**

For additional information, go to <a href="http://www.xilinx.com/support">http://www.xilinx.com/support</a>. The following table lists some of the resources you can access from this website. You can also directly access these resources using the provided URLs.

| Resource             | Description/URL                                                                                                                                                           |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tutorials            | Tutorials covering Xilinx design flows, from design entry to verification and debugging                                                                                   |

|                      | http://www.xilinx.com/support/techsup/tutorials/index.htm                                                                                                                 |

| Answer Browser       | Database of Xilinx solution records <a href="http://www.xilinx.com/xlnx/xil_ans_browser.jsp">http://www.xilinx.com/xlnx/xil_ans_browser.jsp</a>                           |

| Application<br>Notes | Descriptions of device-specific design techniques and approaches <a href="http://www.xilinx.com/apps/appsweb.htm">http://www.xilinx.com/apps/appsweb.htm</a>              |

| Problem Solvers      | Interactive tools that allow you to troubleshoot your design issues<br>http://www.xilinx.com/support/troubleshoot/psolvers.htm                                            |

| Tech Tips            | Latest news, design tips, and patch information for the Xilinx design environment <a href="http://www.xilinx.com/xlnx/xil">http://www.xilinx.com/xlnx/xil</a> tt home.jsp |

### **Conventions**

This document uses the following conventions. An example illustrates each convention.

### **Typographical**

The following typographical conventions are used in this document:

| Convention          | Meaning or Use                                                                                                | Example                                                                                            |

|---------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Courier font        | Messages, prompts, and program files that the system displays                                                 | speed grade: - 100                                                                                 |

| Courier bold        | Literal commands that you enter in a syntactical statement                                                    | ngdbuild design_name                                                                               |

| Helvetica bold      | Commands that you select from a menu                                                                          | File → Open                                                                                        |

|                     | Keyboard shortcuts                                                                                            | Ctrl+C                                                                                             |

| Italic font         | Variables in a syntax statement for which you must supply values                                              | ngdbuild design_name                                                                               |

|                     | References to other manuals                                                                                   | See the <i>Development System Reference Guide</i> for more information.                            |

|                     | Emphasis in text                                                                                              | If a wire is drawn so that it overlaps the pin of a symbol, the two nets are <i>not</i> connected. |

| Square brackets [ ] | An optional entry or parameter.<br>However, in bus specifications,<br>such as bus[7:0], they are<br>required. | ngdbuild [option_name] design_name                                                                 |

| Braces { }          | A list of items from which you must choose one or more                                                        | lowpwr ={on off}                                                                                   |

| Vertical bar        | Separates items in a list of choices                                                                          | <pre>lowpwr ={on off}</pre>                                                                        |

| Vertical ellipsis   | Repetitive material that has been omitted                                                                     | IOB #1: Name = QOUT' IOB #2: Name = CLKIN'                                                         |

| Horizontal ellipsis | Repetitive material that has been omitted                                                                     | allow block block_name loc1 loc2 locn;                                                             |

### **Online Document**

The following conventions are used in this document:

| Convention            | Meaning or Use                                             | Example                                                                                     |

|-----------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Blue text             | Cross-reference link to a location in the current document | See the section "Additional Resources" for details.                                         |

| Red text              | Cross-reference link to a location in another document     | See Figure 2-5 in the <i>Virtex-II</i> Handbook.                                            |

| Blue, underlined text | Hyperlink to a website (URL)                               | Go to <a href="http://www.xilinx.com">http://www.xilinx.com</a> for the latest speed files. |

### Introduction

Xilinx maintains software libraries containing hundreds of functional design elements (primitives and macros) for different device architectures. New functional elements are assembled with each release of development system software. The catalog of design elements is known as the Xilinx Unified Libraries. Elements in these libraries are common to multiple Xilinx device architectures. This "unified" approach means that you can use your circuit design created with "unified" library elements across many current Xilinx device architectures that recognize the element you are using.

Elements that exist in multiple architectures look and function the same, but their implementations might differ to make them more efficient for a particular architecture. A separate library still exists for each architecture and several hundred design elements (primitives and macros) are available across multiple device architectures, providing a common base for programmable logic designs.

If you have active designs that were created with former Xilinx library primitives or macros, you may need to change references to the design elements that you were using to reflect the Unified Libraries elements.

During 2004, libraries guides began to be published only for the latest available architectures (e.g., Virtex-4, Spartan-3E, etc.). This architecture-specific approach is also published in a two-volume set: one for designers who prefer to use hardware description language (HDL), and one for those who prefer to use schematics.

A compendium of the same kind of information for all the most recent architectures continues to be provided as part of the Integrated Software Environment (ISE) program.

The *Spartan-3E Libraries Guide* describes the primitive and macro logic elements supported under the Spartan-3E architecture. Common logic functions can be implemented with these elements and more complex functions can be built by combining macros and primitives.

### **Functional Categories**

The functional categories list the available design elements in each category along with a brief description of each element that is supported under each Xilinx architecture.

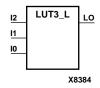

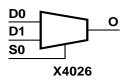

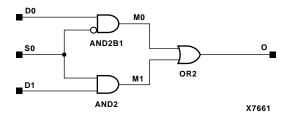

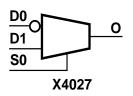

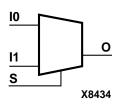

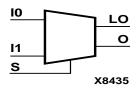

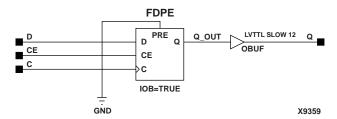

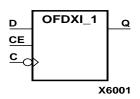

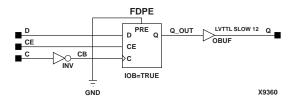

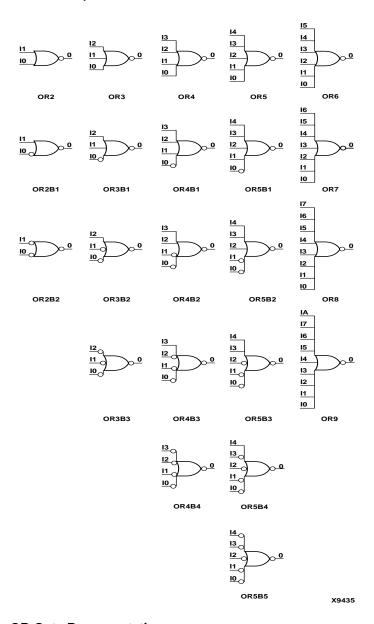

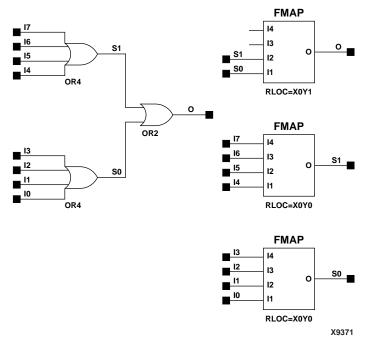

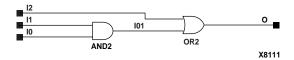

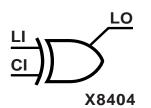

### **Schematic Symbols**

Schematic symbols are included for each device library, and these schematics are illustrated on the first page of the written description of each element in this guide.

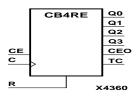

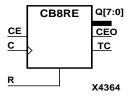

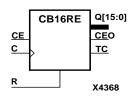

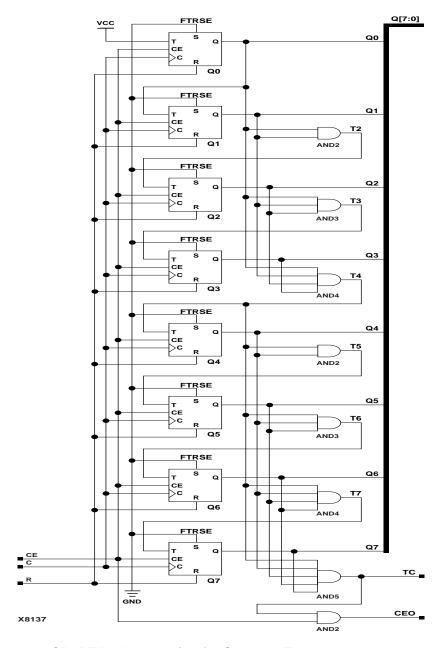

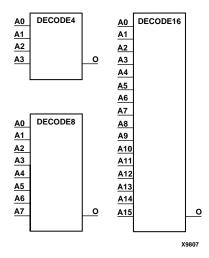

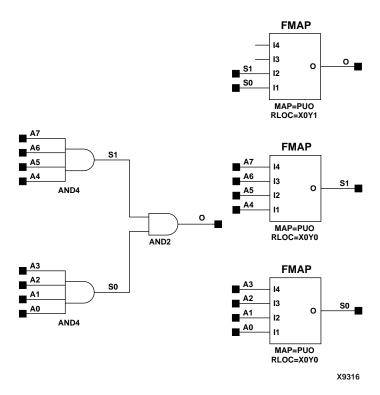

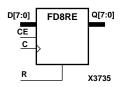

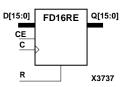

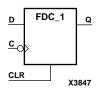

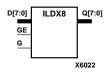

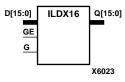

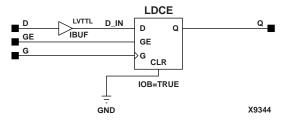

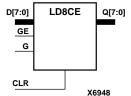

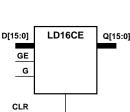

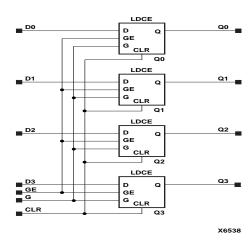

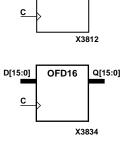

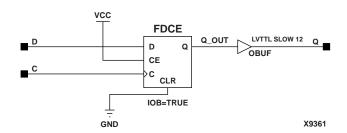

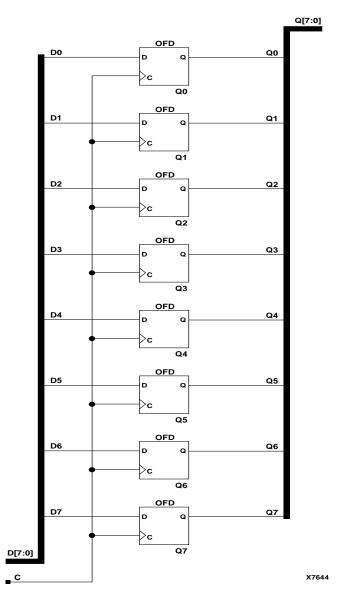

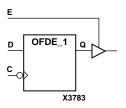

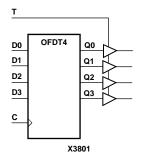

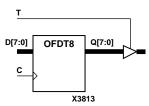

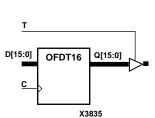

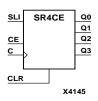

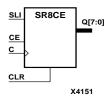

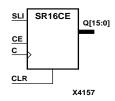

Design elements with bussed or multiple I/O pins (2-, 4-, 8-, 16-bit versions) typically include just one schematic -- generally the 8-bit version. When only one schematic is included, implementation of the smaller and larger elements differs only in the number of sections. In cases where an 8-bit version is very large, an appropriate smaller element serves as the schematic example.

### **Naming Conventions**

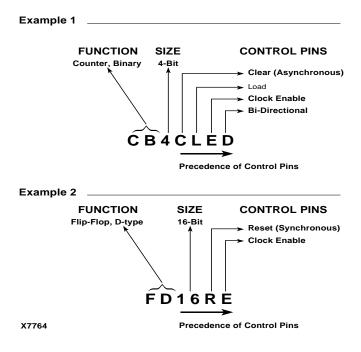

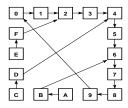

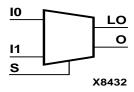

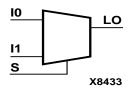

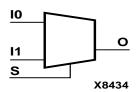

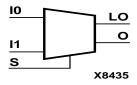

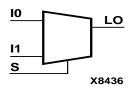

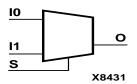

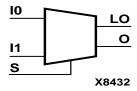

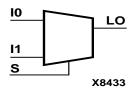

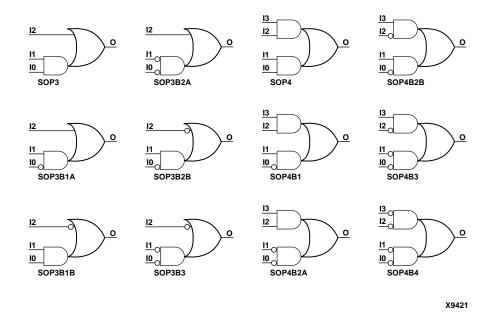

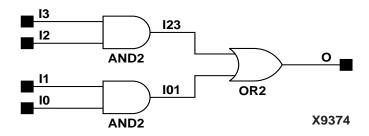

Examples of the general naming conventions for the unified library elements are shown in the following figures.

#### **Naming Conventions**

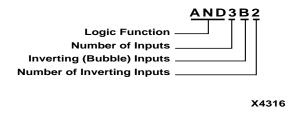

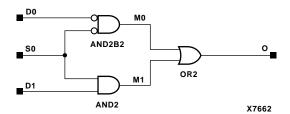

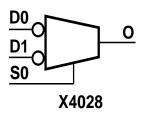

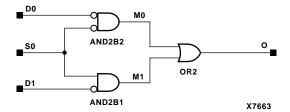

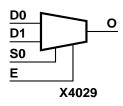

#### **Combinatorial Naming Conventions**

### **Attributes and Constraints**

Attributes are characteristics that help define the functionality of primitive elements. Where appropriate, an "Available Attributes" table is included in the individual descriptions of design elements. Constraints are instructions placed on components, or nets, to indicate their placement, implementation, optimization, and so forth. The Constraints Guide provides additional information about constraints and certain attributes.

# **Table of Contents**

| About this Guide                     |    |

|--------------------------------------|----|

| Guide Contents                       | 3  |

| Additional Resources                 | 3  |

| Conventions                          | 4  |

| Typographical                        |    |

| Online Document                      |    |

| Introduction                         |    |

| Functional Categories                |    |

| Schematic Symbols                    |    |

| Naming Conventions                   |    |

| Attributes and Constraints           | 6  |

| Functional Categories                |    |

| Arithmetic Functions                 | 13 |

| Clock Components                     | 13 |

| Comparators                          | 13 |

| Config/BSCAN                         | 14 |

| Counters                             | 14 |

| Decoders                             | 15 |

| General                              | 15 |

| I/O Components                       | 15 |

| Internal Buffers                     | 16 |

| Logic Gates                          | 16 |

| MUXes                                | 17 |

| RAM/ROM                              | 18 |

| Registers & Latches                  | 18 |

| Shift Registers                      | 21 |

| Slice/CLB Primitives                 | 21 |

| About the Spartan-3E Design Elements |    |

| ACC4, 8, 16                          | 25 |

| ADD4, 8, 16                          |    |

| ADSU4, 8, 16                         |    |

| AND2-9                               |    |

| AND12, 16                            |    |

| BRLSHFT4, 8                          |    |

| BSCAN_SPARTAN3                       |    |

| BUF                                  |    |

| BUFG                                 |    |

| BUFGCE                               |    |

| BUFGCE_1                             |    |

| BUFGMUX                              |    |

| BUFGMUX_1 53                       |

|------------------------------------|

| CAPTURE_SPARTAN3                   |

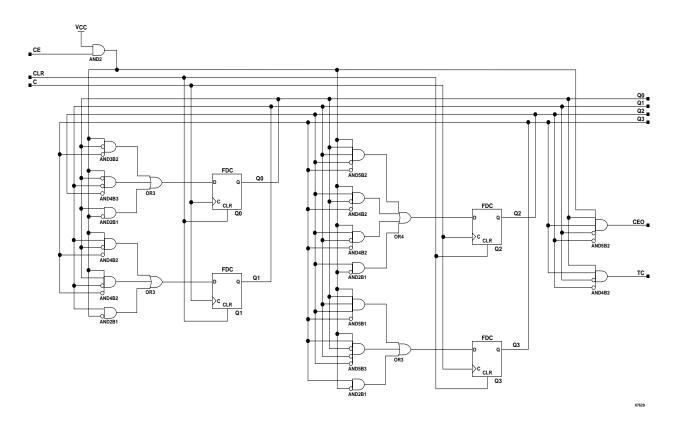

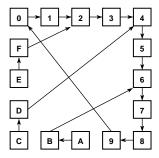

| <b>CB2CE, CB4CE, CB8CE, CB16CE</b> |

| <b>CB2RE, CB4RE, CB8RE, CB16RE</b> |

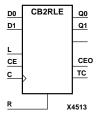

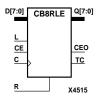

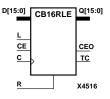

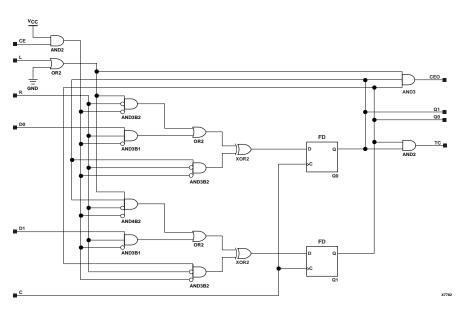

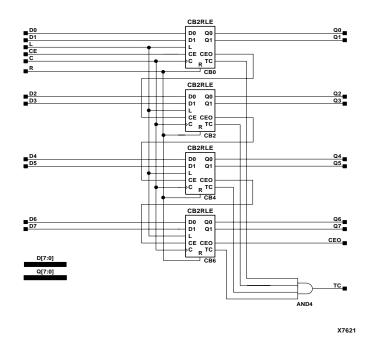

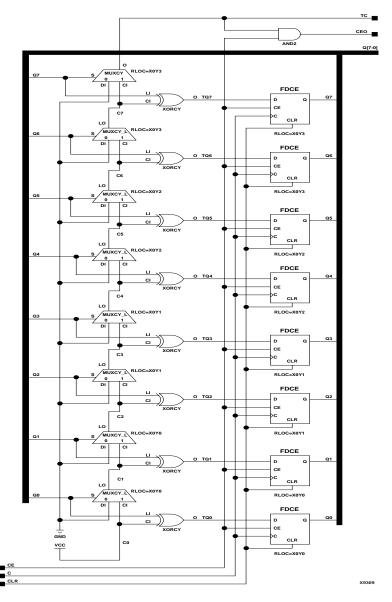

| CB2RLE, CB4RLE, CB8RLE, CB16RLE    |

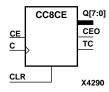

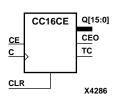

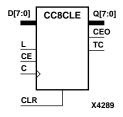

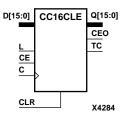

| <b>CC8CE, CC16CE</b>               |

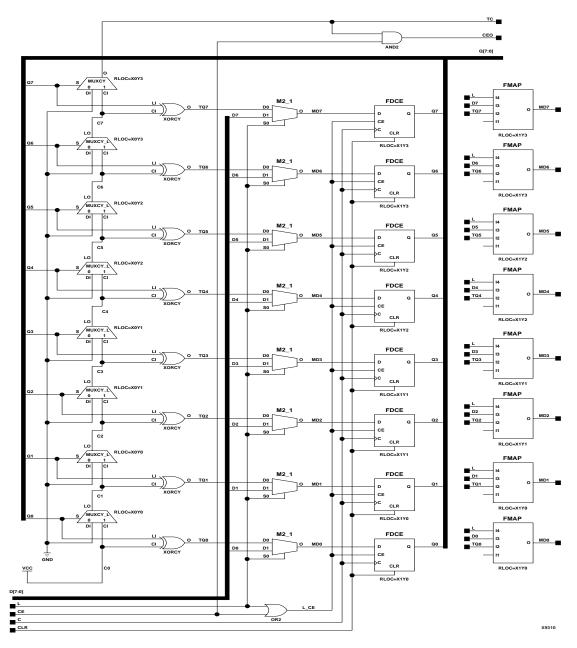

| <b>CC8CLE, CC16CLE</b>             |

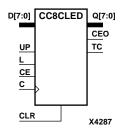

| <b>CC8CLED, CC16CLED</b>           |

| <b>CC8RE, CC16RE</b>               |

| <b>CD4CE</b>                       |

| <b>CD4CLE</b>                      |

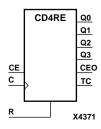

| <b>CD4RE</b> 77                    |

| <b>CD4RLE</b> 79                   |

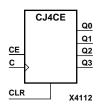

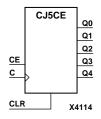

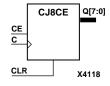

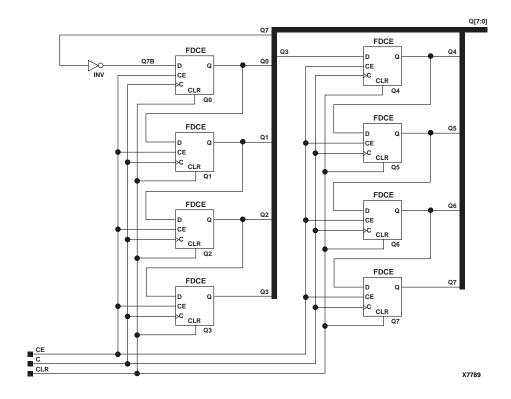

| <b>CJ4CE, CJ5CE, CJ8CE</b>         |

| <b>CJ4RE, CJ5RE, CJ8RE</b>         |

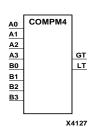

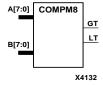

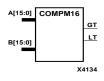

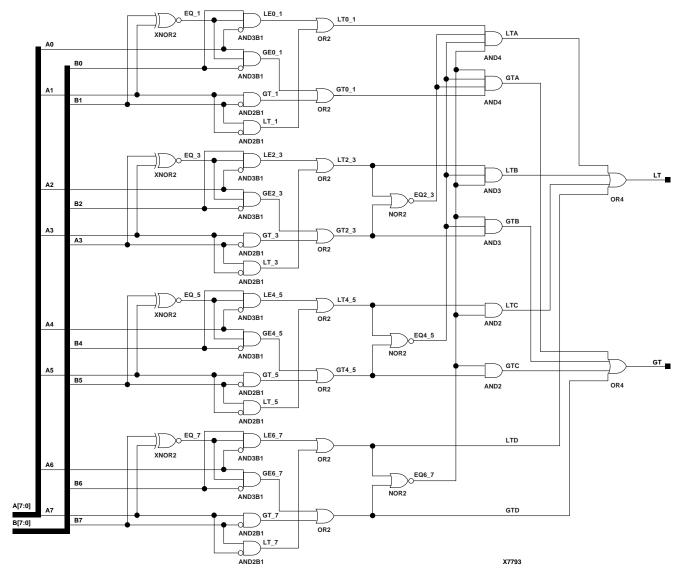

| COMP2, 4, 8, 16                    |

| COMPM2, 4, 8, 16                   |

| <b>COMPMC8, 16</b>                 |

| <b>CR8CE, CR16CE</b> 93            |

| <b>D2_4E</b> 95                    |

| <b>D3_8E</b> 97                    |

| <b>D4_16E</b>                      |

| <b>DCM</b> 101                     |

| <b>DEC_CC4, 8, 16</b>              |

| <b>DECODE4, 8, 16</b>              |

| <b>DECODE32, 64</b>                |

| <b>FD</b>                          |

| <b>FD_1</b>                        |

| <b>FD4CE, FD8CE, FD16CE</b>        |

| <b>FD4RE, FD8RE, FD16RE</b>        |

| FDC                                |

| FDC_1                              |

| FDCE                               |

| FDCE_1                             |

| FDCP                               |

| <b>FDCP_1</b>                      |

| <b>FDCPE</b>                       |

| <b>FDCPE_1</b>                     |

| <b>FDE</b>                         |

| FDE_1                              |

| <b>FDP</b>                         |

| FDP 1                              |

| FDPE           | 145 |

|----------------|-----|

| FDPE_1         | 147 |

| FDR            | 149 |

| FDR_1          | 151 |

| FDRE           | 153 |

| FDRE_1         | 155 |

| FDRS           | 157 |

| FDRS_1         | 159 |

| FDRSE          | 161 |

| FDRSE_1        | 163 |

| FDS            | 165 |

| FDS_1          | 167 |

| FDSE           | 169 |

| FDSE_1         | 171 |

| FJKC           | 173 |

| FJKCE          | 175 |

| FJKP           | 177 |

| FJKPE          | 179 |

| FJKRSE         | 181 |

| FJKSRE         | 183 |

| FTC            | 185 |

| FTCE           | 187 |

| FTCLE          |     |

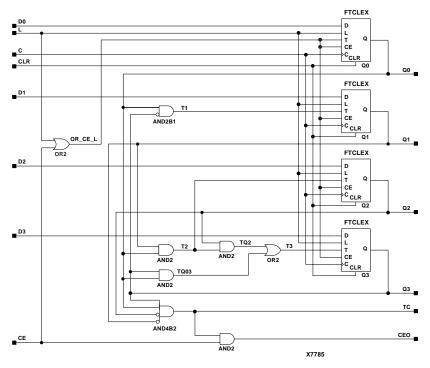

| FTCLEX         | 191 |

| FTP            |     |

| FTPE           | 195 |

| FTPLE          | 197 |

| FTRSE          | 199 |

| FTRSLE         | 201 |

| FTSRE          | 203 |

| FTSRLE         |     |

| GND            | 207 |

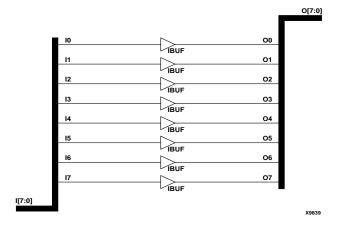

| IBUF, 4, 8, 16 | 209 |

| IBUFDS         | 211 |

| IBUFG          |     |

| IBUFGDS        | 215 |

| IDDR2          | 217 |

| IFD, 4, 8, 16  | 219 |

| IFD_1          |     |

| IFDI           |     |

| IFDI_1         |     |

| IFDX 1         | 229 |

| IFDX, 4, 8, 16                 | 231 |

|--------------------------------|-----|

| IFDXI_1                        | 235 |

| IFDXI                          | 237 |

| ILD_1                          | 239 |

| ILD, 4, 8, 16                  | 241 |

| ILDI                           | 245 |

| ILDI_1                         | 247 |

| ILDX_1                         | 249 |

| ILDX, 4, 8, 16                 | 251 |

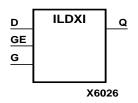

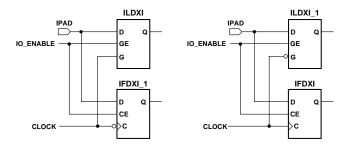

| ILDXI                          | 255 |

| ILDXI_1                        | 257 |

| INV, 4, 8, 16                  | 259 |

| IOBUF                          | 261 |

| IOBUFDS                        | 263 |

| KEEPER                         | 265 |

| LD                             | 267 |

| LD_1                           | 269 |

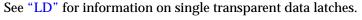

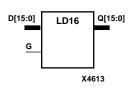

| LD4, 8, 16                     | 271 |

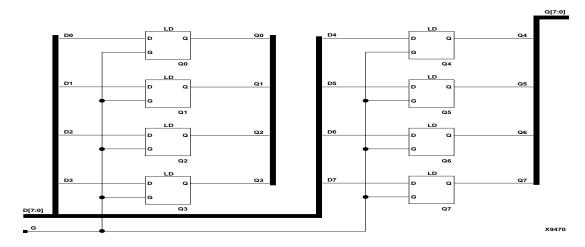

| LD4CE, LD8CE, LD16CE           | 273 |

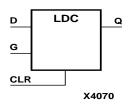

| LDC                            | 275 |

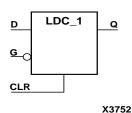

| LDC_1                          | 277 |

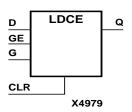

| LDCE                           | 279 |

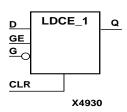

| LDCE_1                         | 281 |

| LDCP                           | 283 |

| LDCP_1                         | 285 |

| LDCPE                          | 287 |

| LDCPE_1                        | 289 |

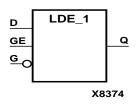

| LDE                            | 291 |

| LDE_1                          | 293 |

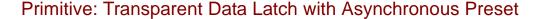

| LDP                            | 295 |

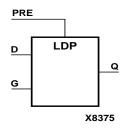

| LDP_1                          | 297 |

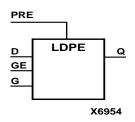

| LDPE                           |     |

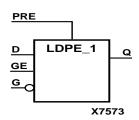

| LDPE_1                         | 301 |

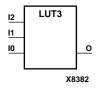

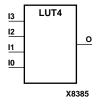

| LUT1, 2, 3, 4                  | 303 |

| LUT1_D, LUT2_D, LUT3_D, LUT4_D | 305 |

| LUT1_L, LUT2_L, LUT3_L, LUT4_L | 307 |

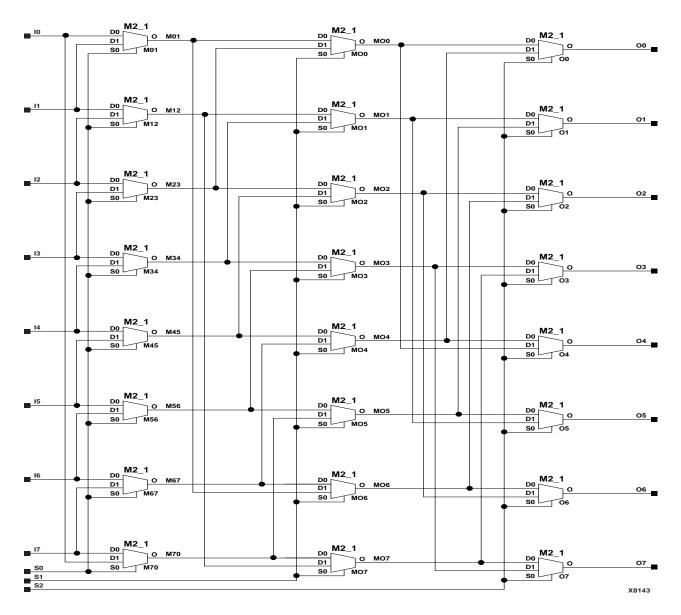

| M2_1                           | 309 |

| M2_1B1                         |     |

| M2_1B2                         | 313 |

| M2_1E                          | 315 |

| M4_1E                          | 317 |

| M8 1E                          | 319 |

| M16_1E 32       |            |

|-----------------|------------|

| MULT_AND        | 23         |

| MULT18X18SIO    |            |

| MUXCY           | 27         |

| MUXCY_D         | 29         |

| MUXCY_L         | 31         |

| MUXF5           | 33         |

| MUXF5_D         | 35         |

| MUXF5_L         | 37         |

| MUXF6           | 39         |

| MUXF6_D         | ł 1        |

| MUXF6_L 34      | 13         |

| MUXF7           | <b>1</b> 5 |

| MUXF7_D         | Į7         |

| MUXF7_L         | 19         |

| MUXF8           | <b>i</b> 1 |

| MUXF8_D         | <b>i</b> 3 |

| MUXF8_L         | 55         |

| NAND2-9         |            |

| NAND12, 16      | <b>j</b> 9 |

| NOR2-9          | 31         |

| NOR12, 16       | 3          |

| OBUF, 4, 8, 16  | 35         |

| <b>OBUFDS</b>   | 37         |

| OBUFT, 4, 8, 16 |            |

| OBUFTDS 37      | 1          |

| <b>ODDR2</b>    | /3         |

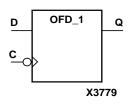

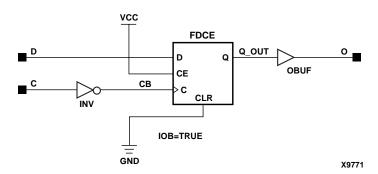

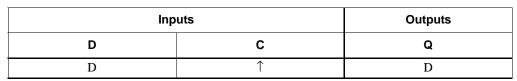

| OFD_1           | 15         |

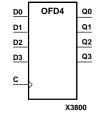

| OFD, 4, 8, 16   |            |

| OFDE_1          |            |

| OFDE, 4, 8, 16  |            |

| OFDI            |            |

| OFDI_1          | 35         |

| OFDT_1          | 37         |

| OFDT, 4, 8, 16  | 39         |

| OFDX_1          | )1         |

| OFDX, 4, 8, 16  | )3         |

| <b>OFDXI</b>    |            |

| <b>OFDXI_1</b>  |            |

| OR2-9           | )9         |

| OR12, 16        | )1         |

| PULLDOWN 40     | )3         |

| <b>PULLUP</b>                     |

|-----------------------------------|

| <b>RAM16X1D</b>                   |

| <b>RAM16X1D_1</b>                 |

| <b>RAM16X1S</b>                   |

| <b>RAM16X1S_1</b>                 |

| <b>RAM16X2S</b>                   |

| <b>RAM16X4S</b>                   |

| <b>RAM32X1S</b>                   |

| <b>RAM32X1S_1</b> 421             |

| <b>RAM32X2S</b>                   |

| <b>RAM64X1S</b>                   |

| <b>RAM64X1S_1</b>                 |

| <b>ROM16X1</b>                    |

| <b>ROM32X1</b>                    |

| <b>ROM64X1</b>                    |

| <b>ROM128X1</b>                   |

| <b>ROM256X1</b>                   |

| SOP3-4                            |

| <b>SR4CE, SR8CE, SR16CE</b>       |

| <b>SR4CLE, SR8CLE, SR16CLE</b>    |

| <b>SR4CLED, SR8CLED, SR16CLED</b> |

| <b>SR4RE, SR8RE, SR16RE</b>       |

| <b>SR4RLE, SR8RLE, SR16RLE</b>    |

| <b>SR4RLED, SR8RLED, SR16RLED</b> |

| <b>SRL16</b>                      |

| SRL16_1                           |

| <b>SRL16E</b>                     |

| SRL16E_1                          |

| SRLC16                            |

| SRLC16_1                          |

| SRLC16E                           |

| <b>SRLC16E_1</b>                  |

| STARTUP_SPARTAN3E                 |

| VCC                               |

| XNOR2-9                           |

| <b>XOR2-9</b>                     |

| <b>XORCY</b>                      |

| <b>XORCY_D</b>                    |

| <b>XORCY_L</b>                    |

# Functional Categories

This section categorizes, by function, the design elements that are described in detail later in this guide. The elements (primitive and macro implementations) are listed in alphanumeric order under each functional category.

Arithmetic Functions Decoders MUXes

Clock Components General RAM/ROM

Comparators I/O Components Registers & Latches

Config/BSCAN Internal Buffers Shift Registers

Counters Logic Gates Slice/CLB Primitives

### **Arithmetic Functions**

| Design Element | Description                                                                                                                 |

|----------------|-----------------------------------------------------------------------------------------------------------------------------|

| ACC4           | Macro : 4-Bit Loadable Cascadable Accumulator with Carry-In, Carry-Out, and Synchronous Reset                               |

| ACC8           | Macro : 8-Bit Loadable Cascadable Accumulator with Carry-In, Carry-Out, and Synchronous Reset                               |

| ACC16          | Macro : 16-Bit Loadable Cascadable Accumulator with Carry-In, Carry-Out, and Synchronous Reset                              |

| ADD4           | Macro : 4-Bit Cascadable Full Adder with Carry-In, Carry-Out, and Overflow                                                  |

| ADD8           | Macro : 8-Bit Cascadable Full Adder with Carry-In, Carry-Out, and Overflow                                                  |

| ADD16          | Macro : 16-Bit Cascadable Full Adder with Carry-In, Carry-Out, and Overflow                                                 |

| ADSU4          | Macro : 4-Bit Cascadable Adder/Subtracter with Carry-In, Carry-Out, and Overflow                                            |

| ADSU8          | Macro: 8-Bit Cascadable Adder/Subtracter with Carry-In, Carry-Out, and Overflow                                             |

| ADSU16         | Macro : 16-Bit Cascadable Adder/Subtracter with Carry-In, Carry-Out, and Overflow                                           |

| MULT18X18SIO   | Primitive: 18x18 Cascadable Signed Multiplier with Optional Input and Output registers, Clock Enable, and Synchronous Reset |

### **Clock Components**

| Design Element | Description                                                              |

|----------------|--------------------------------------------------------------------------|

| BUFG           | Primitive : Global Clock Buffer                                          |

| BUFGCE         | Primitive : Global Clock MUX with Clock Enable and Output State 0        |

| BUFGCE_1       | Primitive : Global Clock MUX Buffer with Clock Enable and Output State 1 |

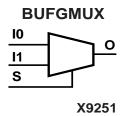

| BUFGMUX        | Primitive : Global Clock MUX Buffer with Output State 0                  |

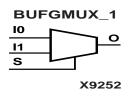

| BUFGMUX_1      | Primitive : Global Clock MUX with Output State 1                         |

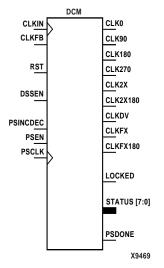

| DCM            | Primitive: Digital Clock Manager                                         |

### **Comparators**

| Design Element | Description                       |

|----------------|-----------------------------------|

| COMP2          | Macro : 2-Bit Identity Comparator |

| COMP4          | Macro : 4-Bit Identity Comparator |

| Design Element | Description                         |

|----------------|-------------------------------------|

| COMP8          | Macro : 8-Bit Identity Comparator   |

| COMP16         | Macro: 16-Bit Identity Comparator   |

| COMPM2         | Macro : 2-Bit Magnitude Comparator  |

| COMPM4         | Macro : 4-Bit Magnitude Comparator  |

| COMPM8         | Macro : 8-Bit Magnitude Comparator  |

| COMPM16        | Macro : 16-Bit Magnitude Comparator |

| COMPMC8        | Macro : 8-Bit Magnitude Comparator  |

| COMPMC16       | Macro : 16-Bit Magnitude Comparator |

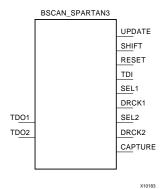

# Config/BSCAN

| Design Element    | Description                                                                                                           |

|-------------------|-----------------------------------------------------------------------------------------------------------------------|

| BSCAN_SPARTAN3    | Primitive : Spartan-3 Boundary Scan Logic Control Circuit                                                             |

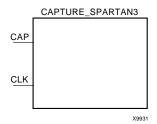

| CAPTURE_SPARTAN3  | Primitive: Spartan-3 Register State Capture for Bitstream Readback                                                    |

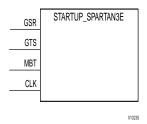

| STARTUP_SPARTAN3E | Primitive: Spartan-3E User Interface to the GSR, GTS, Configuration Startup Sequence and Multi-Boot Trigger Circuitry |

# **Counters**

| Design Element | Description                                                                                              |

|----------------|----------------------------------------------------------------------------------------------------------|

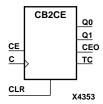

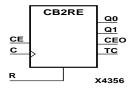

| CB2CE          | Macro : 2-Bit Cascadable Binary Counter with Clock Enable and Asynchronous Clear                         |

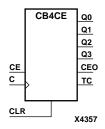

| CB4CE          | Macro : 4-Bit Cascadable Binary Counter with Clock Enable and Asynchronous Clear                         |

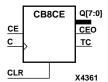

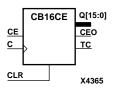

| CB8CE          | Macro : 8-Bit Cascadable Binary Counter with Clock Enable and Asynchronous Clear                         |

| CB16CE         | Macro : 16-Bit Cascadable Binary Counter with Clock Enable and Asynchronous Clear                        |

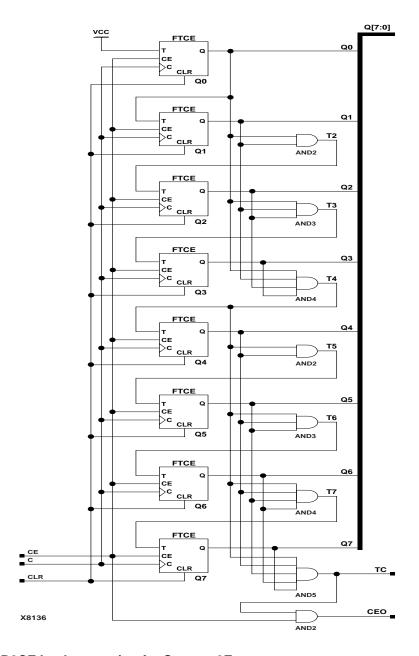

| CB2RE          | Macro : 2-Bit Cascadable Binary Counter with Clock Enable and Synchronous Reset                          |

| CB4RE          | Macro : 4-Bit Cascadable Binary Counter with Clock Enable and Synchronous Reset                          |

| CB8RE          | Macro : 8-Bit Cascadable Binary Counter with Clock Enable and Synchronous Reset                          |

| CB16RE         | Macro : 16-Bit Cascadable Binary Counter with Clock Enable and Synchronous Reset                         |

| CB2RLE         | Macro : 2-Bit Loadable Cascadable Binary Counter with Clock Enable and Synchronous Reset                 |

| CB4RLE         | Macro : 4-Bit Loadable Cascadable Binary Counter with Clock Enable and Synchronous Reset                 |

| CB8RLE         | Macro : 8-Bit Loadable Cascadable Binary Counter with Clock Enable and Synchronous Reset                 |

| CB16RLE        | Macro : 16-Bit Loadable Cascadable Binary Counter with Clock Enable and Synchronous Reset                |

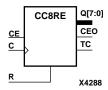

| CC8CE          | Macro : 8-Bit Cascadable Binary Counter with Clock Enable and Asynchronous Clear                         |

| CC16CE         | Macro : 16-Bit Cascadable Binary Counter with Clock Enable and Asynchronous Clear                        |

| CC8CLE         | Macro : 8-Bit Loadable Cascadable Binary Counter with Clock Enable and Asynchronous Clear                |

| CC16CLE        | Macro : 16-Bit Loadable Cascadable Binary Counter with Clock Enable and Asynchronous Clear               |

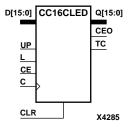

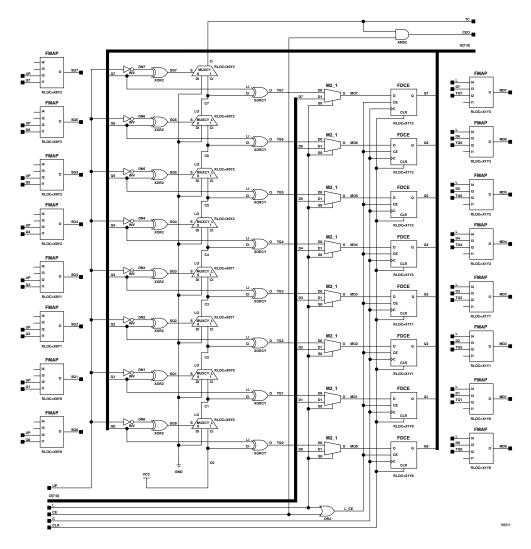

| CC8CLED        | Macro : 8-Bit Loadable Cascadable Bidirectional Binary Counter with Clock Enable and Asynchronous Clear  |

| CC16CLED       | Macro : 16-Bit Loadable Cascadable Bidirectional Binary Counter with Clock Enable and Asynchronous Clear |

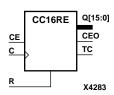

| CC8RE          | Macro : 8-Bit Cascadable Binary Counter with Clock Enable and Synchronous Reset                          |

| CC16RE         | Macro : 16-Bit Cascadable Binary Counter with Clock Enable and Synchronous Reset                         |

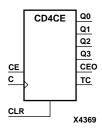

| CD4CE          | Macro : 4-Bit Cascadable BCD Counter with Clock Enable and Asynchronous Clear                            |

| CD4CLE         | Macro : 4-Bit Loadable Cascadable BCD Counter with Clock Enable and Asynchronous Clear                   |

| CD4RE          | Macro : 4-Bit Cascadable BCD Counter with Clock Enable and Synchronous Reset                             |

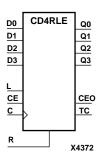

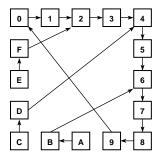

| CD4RLE         | Macro : 4-Bit Loadable Cascadable BCD Counter with Clock Enable and Synchronous Reset                    |

| CJ4CE          | Macro : 4-Bit Johnson Counter with Clock Enable and Asynchronous Clear                                   |

| CJ5CE          | Macro : 5-Bit Johnson Counter with Clock Enable and Asynchronous Clear                                   |

| CJ8CE          | Macro : 8-Bit Johnson Counter with Clock Enable and Asynchronous Clear                                   |

| CJ4RE          | Macro : 4-Bit Johnson Counter with Clock Enable and Synchronous Reset                                    |

| Design Element | Description                                                                                 |

|----------------|---------------------------------------------------------------------------------------------|

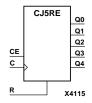

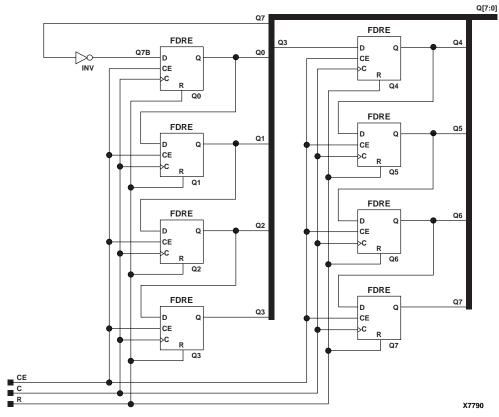

| CJ5RE          | Macro : 5-Bit Johnson Counter with Clock Enable and Synchronous Reset                       |

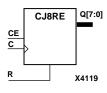

| CJ8RE          | Macro : 8-Bit Johnson Counter with Clock Enable and Synchronous Reset                       |

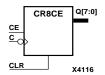

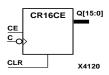

| CR8CE          | Macro : 8-Bit Negative-Edge Binary Ripple Counter with Clock Enable and Asynchronous Clear  |

| CR16CE         | Macro : 16-Bit Negative-Edge Binary Ripple Counter with Clock Enable and Asynchronous Clear |

### **Decoders**

| Design Element | Description                                             |

|----------------|---------------------------------------------------------|

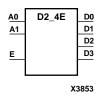

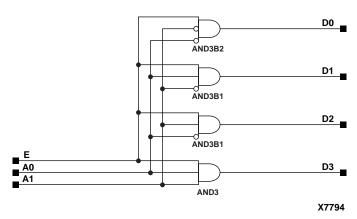

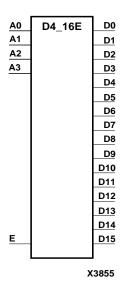

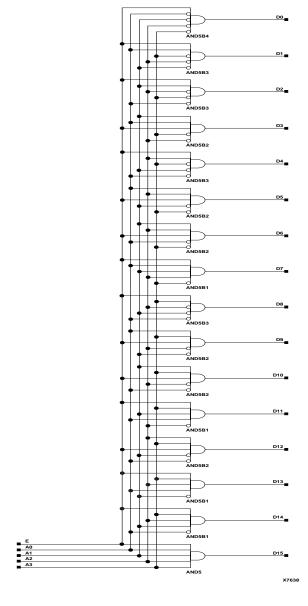

| D2_4E          | Macro : 2- to 4-Line Decoder/Demultiplexer with Enable  |

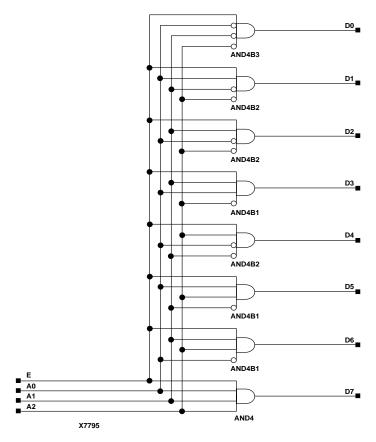

| D3_8E          | Macro : 3- to 8-Line Decoder/Demultiplexer with Enable  |

| D4_16E         | Macro : 4- to 16-Line Decoder/Demultiplexer with Enable |

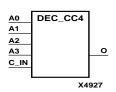

| DEC_CC4        | Macro : 4-Bit Active Low Decoder                        |

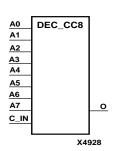

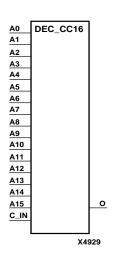

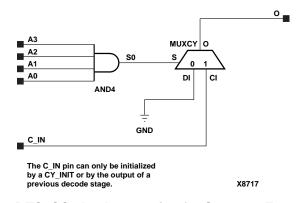

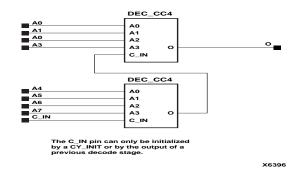

| DEC_CC8        | Macro: 8-Bit Active Low Decoder                         |

| DEC_CC16       | Macro: 16-Bit Active Low Decoder                        |

| DECODE4        | Macro: 4-Bit Active-Low Decoder                         |

| DECODE8        | Macro: 8-Bit Active-Low Decoder                         |

| DECODE16       | Macro: 16-Bit Active-Low Decoder                        |

| DECODE32       | Macro: 32-Bit Active-Low Decoder                        |

| DECODE64       | Macro: 64-Bit Active-Low Decoder                        |

### **General**

| Design Element | Description                              |

|----------------|------------------------------------------|

| GND            | Primitive : Ground-Connection Signal Tag |

| VCC            | Primitive: Vcc-Connection Signal Tag     |

# **I/O Components**

| Design Element | Description                                                                                                                                     |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| IBUF           | Primitive: Single-Ended Input Buffer                                                                                                            |

| IBUF4          | Macro: Multiple-Input Buffer                                                                                                                    |

| IIBUF8         | Macro: Multiple-Input Buffer                                                                                                                    |

| IBUF16         | Macro: Multiple-Input Buffer                                                                                                                    |

| IBUFDS         | Primitive : Differential Signaling Input Buffer with Selectable I/O Interface                                                                   |

| IBUFG          | Primitive : Dedicated Input Buffer with Selectable I/O Interface                                                                                |

| IBUFGDS        | Primitive : Dedicated Differential Signaling Input Buffer with Selectable I/O Interface                                                         |

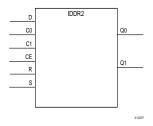

| IDDR2          | Primitive: Double Data Rate Input D Flip-Flop with Optional Data Alignment, Clock Enable and Programmable Synchronous or Asynchronous Set/Reset |

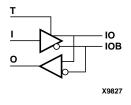

| IOBUF          | Primitive : Bi-Directional Buffer with Selectable I/0 Interface (multiple primitives)                                                           |

| IOBUFDS        | Primitive : 3-State Differential Signaling I/O Buffer with Active Low Output Enable                                                             |

| KEEPER         | Primitive : KEEPER Symbol                                                                                                                       |

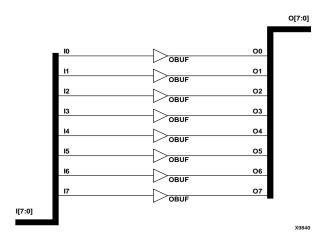

| OBUF           | Primitive : Single- and Multiple-Output Buffer                                                                                                  |

| OBUF4          | Macro : Multiple-Output Buffer                                                                                                                  |

| OBUF8          | Macro : Multiple-Output Buffer                                                                                                                  |

| OBUF16         | Macro : Multiple-Output Buffer                                                                                                                  |

| OBUFDS         | Primitive : Differential Signaling Output Buffer with Selectable I/O Interface                                                                  |

| OBUFT          | Primitive : Single and Multiple 3-State Output Buffer with Active Low Output Enable                                                             |

| Design Element | Description                                                                                                                                    |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------|

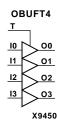

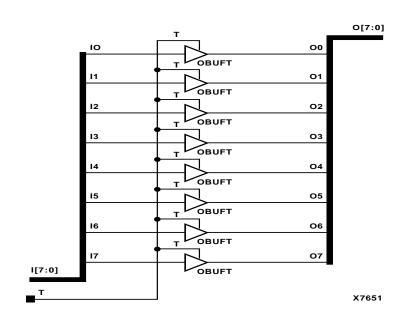

| OBUFT4         | Macro : Single and Multiple 3-State Output Buffer with Active Low Output Enable                                                                |

| OBUFT8         | Macro : Single and Multiple 3-State Output Buffer with Active Low Output Enable                                                                |

| OBUFT16        | Macro : Single and Multiple 3-State Output Buffer with Active Low Output Enable                                                                |

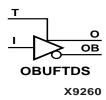

| OBUFTDS        | Primitive : 3-State Output Buffer with Differential Signaling, Active-Low Output Enable, and Selectable I/O Interface                          |

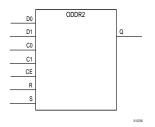

| ODDR2          | Primitive: Dual Data Rate Output D Flip-Flop with Optional Data Alignment, Clock Enable and Programmable Synchronous or Asynchronous Set/Reset |

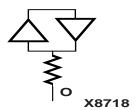

| PULLDOWN       | Primitive : Resistor to GND for Input Pads                                                                                                     |

| PULLUP         | Primitive : Resistor to VCC for Input PADs, Open-Drain, and 3-State Outputs                                                                    |

### **Internal Buffers**

| Design Element | Description                        |

|----------------|------------------------------------|

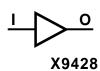

| BUF            | Primitive : General Purpose Buffer |

### **Logic Gates**

| Design Element | Description                                                         |

|----------------|---------------------------------------------------------------------|

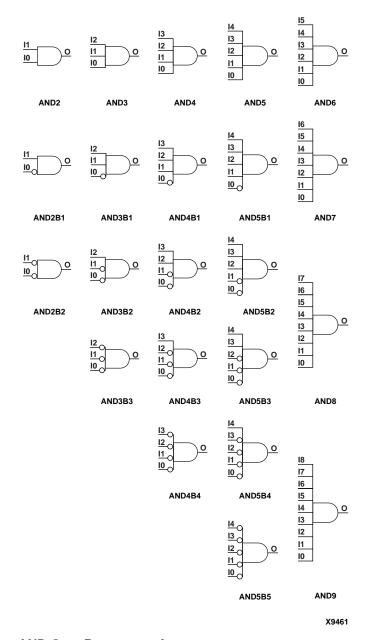

| AND2           | Primitive: 2-Input AND Gate with Inverted and Non-Inverted Inputs   |

| AND3           | Primitive : 3-Input AND Gate with Inverted and Non-Inverted Inputs  |

| AND4           | Primitive : 4-Input AND Gate with Inverted and Non-Inverted Inputs  |

| AND5           | Primitive: 5-Input AND Gate with Inverted and Non-Inverted Inputs   |

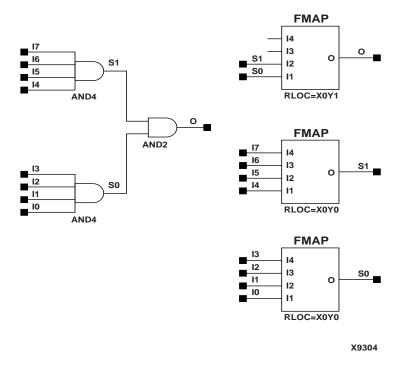

| AND6           | Macro : 6-Input AND Gate with Inverted and Non-Inverted Inputs      |

| AND7           | Macro : 7-Input AND Gate with Inverted and Non-Inverted Inputs      |

| AND8           | Macro: 8-Input AND Gate with Inverted and Non-Inverted Inputs       |

| AND9           | Macro : 9-Input AND Gate with Inverted and Non-Inverted Inputs      |

| AND12          | Macro: 12- Input AND Gate with Non-Inverted Inputs                  |

| AND16          | Macro : 16- Input AND Gate with Non-Inverted Inputs                 |

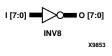

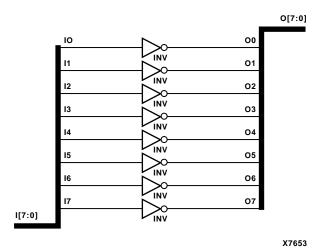

| INV            | Primitive : Single and Multiple Inverters                           |

| INV4           | Macro: Single and Multiple Inverters                                |

| INV8           | Macro : Single and Multiple Inverters                               |

| INV16          | Macro : Single and Multiple Inverters                               |

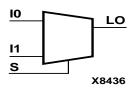

| NAND2          | Primitive :2-Input NAND Gate with Inverted and Non-Inverted Inputs  |

| NAND3          | Primitive : 3-Input NAND Gate with Inverted and Non-Inverted Inputs |

| NAND3B1        | Primitive :3-Input NAND Gate with Inverted and Non-Inverted Inputs  |

| NAND3B2        | Primitive : 3-Input NAND Gate with Inverted and Non-Inverted Inputs |

| NAND3B3        | Primitive : 3-Input NAND Gate with Inverted and Non-Inverted Inputs |

| NAND4          | Primitive : 4-Input NAND Gate with Inverted and Non-Inverted Inputs |

| NAND5          | Macro: 5-Input NAND Gate with Inverted and Non-Inverted Inputs      |

| NAND6          | Macro : 6-Input NAND Gate with Inverted and Non-Inverted Inputs.    |

| NAND7          | Macro : 7-Input NAND Gate with Inverted and Non-Inverted Inputs.    |

| NAND8          | Macro: 8-Input NAND Gate with Inverted and Non-Inverted Inputs.     |

| NAND9          | Macro : 9-Input NAND Gate with Inverted and Non-Inverted Inputs.    |

| NAND12         | Macro: 12- Input NAND Gate with Non-Inverted Inputs.                |

| NAND16         | Macro: 16- Input NAND Gate with Non-Inverted Inputs.                |

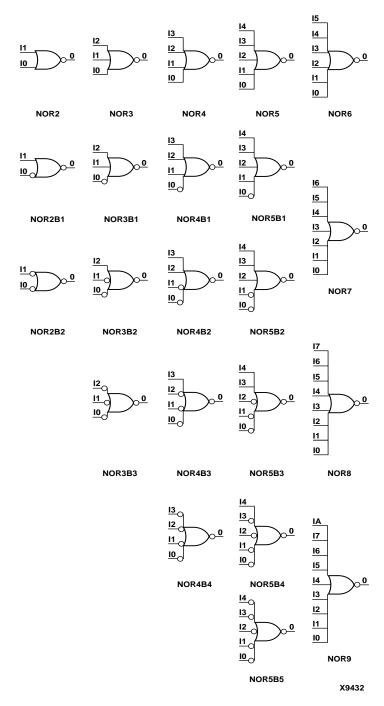

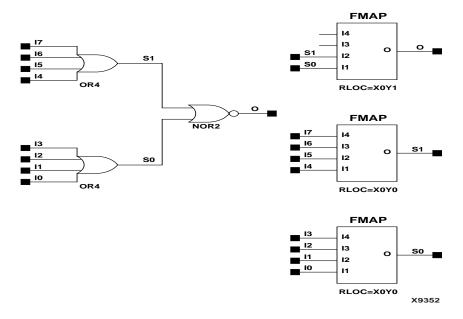

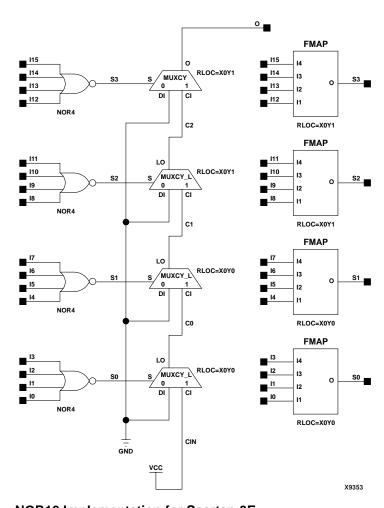

| NOR2           | Primitive: 2- Input NOR Gate with Inverted and Non-Inverted Inputs. |

| NOR3           | Primitive : 3- Input NOR Gate with Inverted and Non-Inverted Inputs |

| NOR4           | Primitive : 4- Input NOR Gate with Inverted and Non-Inverted Inputs |

| NOR6           | Macro : 6- Input NOR Gate with Inverted and Non-Inverted Inputs     |

| Design Element | Description                                                       |

|----------------|-------------------------------------------------------------------|

| NOR7           | Macro : 7- Input NOR Gate with Inverted and Non-Inverted Inputs   |

| NOR8           | Macro: 8- Input NOR Gate with Inverted and Non-Inverted Inputs    |

| NOR9           | Macro: 9- Input NOR Gate with Inverted and Non-Inverted Inputs    |

| NOR12          | Macro: 12-Input NOR Gate with Non-Inverted Inputs                 |

| NOR16          | Macro : 16-Input NOR Gate with Non-Inverted Inputs                |

| OR2            | Primitive : 2-Input OR Gate with Inverted and Non-Inverted Inputs |

| OR3            | Primitive : 3-Input OR Gate with Inverted and Non-Inverted Inputs |

| OR4            | Primitive : 4-Input OR Gate with Inverted and Non-Inverted Inputs |

| OR6            | Macro : 6-Input OR Gate with Inverted and Non-Inverted Inputs     |

| OR7            | Macro : 6-Input OR Gate with Inverted and Non-Inverted Inputs     |

| OR8            | Macro: 8-Input OR Gate with Inverted and Non-Inverted Inputs      |

| OR9            | Macro : 9-Input OR Gate with Inverted and Non-Inverted Inputs     |

| OR12           | Macro : 12-Input OR Gate with Inverted and Non-Inverted Inputs    |

| OR16           | Macro : 16-Input OR Gate with Inverted and Non-Inverted Inputs    |

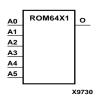

| SOP3           | Macro : Sum of Products                                           |

| SOP3B1A        | Macro : Sum of Products                                           |

| SOP3B1B        | Macro : Sum of Products                                           |

| SOP3B2A        | Macro : Sum of Products                                           |

| SOP3B2B        | Macro : Sum of Products                                           |

| SOP3B3         | Macro : Sum of Products                                           |

| SOP4           | Macro : Sum of Products                                           |

| SOP4B1         | Macro: Sum of Products                                            |

| SOP4B2A        | Macro: Sum of Products                                            |

| SOP4B2B        | Macro : Sum of Products                                           |

| SOP4B3         | Macro: Sum of Products                                            |

| SOP4B4         | Macro : Sum of Products                                           |

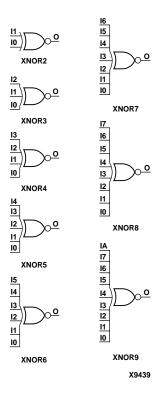

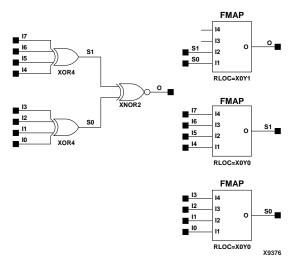

| XNOR2          | Primitive : 2-Input XNOR Gate with Non-Inverted Inputs            |

| XNOR3          | Primitive : 3-Input XNOR Gate with Non-Inverted Inputs            |

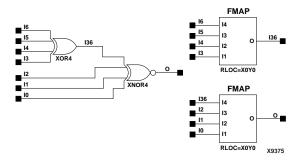

| XNOR4          | Primitive : 4-Input XNOR Gate with Non-Inverted Inputs            |

| XNOR9          | Macro: 9-Input XNOR Gate with Non-Inverted Inputs                 |

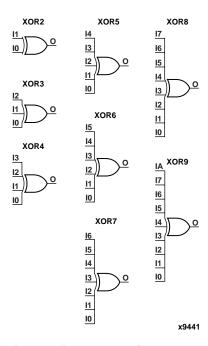

| XOR2           | Macro : 2-Input XOR Gate with Non-Inverted Inputs                 |

| XOR3           | Macro: 3-Input XOR Gate with Non-Inverted Inputs                  |

| XOR4           | Primitive : 4-Input XOR Gate with Non-Inverted Inputs             |

| XOR6           | Macro: 6-Input XOR Gate with Non-Inverted Inputs                  |

| XOR7           | Macro: 7-Input XOR Gate with Non-Inverted Inputs                  |

| XOR9           | Macro: 9-Input XOR Gate with Non-Inverted Inputs                  |

### **MUXes**

| Design Element | Description                                       |

|----------------|---------------------------------------------------|

| M2_1           | Macro : 2-to-1 Multiplexer                        |

| M2_1B1         | Macro: 2-to-1 Multiplexer with D0 Inverted        |

| M2_1B2         | Macro: 2-to-1 Multiplexer with D0 and D1 Inverted |

| M2_1E          | Macro: 2-to-1 Multiplexer with Enable             |

| M4_1E          | Macro: 4-to-1 Multiplexer with Enable             |

| M8_1E          | Macro: 8-to-1 Multiplexer with Enable             |

| M16_1E         | Macro: 16-to-1 Multiplexer with Enable            |

### **RAM/ROM**

| Design Element | Description                                                                             |

|----------------|-----------------------------------------------------------------------------------------|

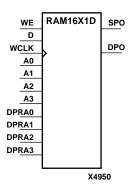

| RAM16X1D       | Primitive : 16-Deep by 1-Wide Static Dual Port Synchronous RAM                          |

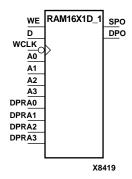

| RAM16X1D_1     | Primitive : 16-Deep by 1-Wide Static Dual Port Synchronous RAM with Negative-Edge Clock |

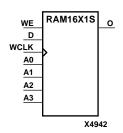

| RAM16X1S       | Primitive : 16-Deep by 1-Wide Static Synchronous RAM                                    |

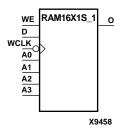

| RAM16X1S_1     | Primitive : 16-Deep by 1-Wide Static Synchronous RAM with Negative-Edge Clock           |

| RAM16X2S       | Macro : 16-Deep by 2-Wide Static Synchronous RAM                                        |

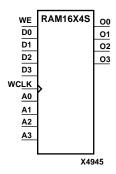

| RAM16X4S       | Macro : 16-Deep by 4-Wide Static Synchronous RAM                                        |

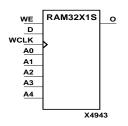

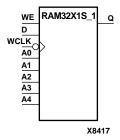

| RAM32X1S       | Primitive: 32-Deep by 1-Wide Static Synchronous RAM                                     |

| RAM32X1S_1     | Primitive: 32-Deep by 1-Wide Static Synchronous RAM with Negative-Edge Clock            |

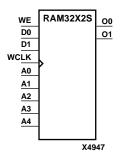

| RAM32X2S       | Primitive: 32-Deep by 2-Wide Static Synchronous RAM                                     |

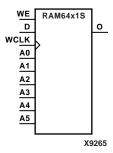

| RAM64X1S       | Primitive: 64-Deep by 1-Wide Static Synchronous RAM                                     |

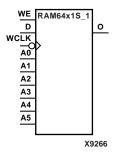

| RAM64X1S_1     | Primitive: 64-Deep by 1-Wide Static Synchronous RAM with Negative-Edge Clock            |

| ROM16X1        | Primitive: 16-Deep by 1-Wide ROM                                                        |

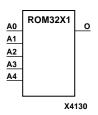

| ROM32X1        | Primitive: 32-Deep by 1-Wide ROM                                                        |

| ROM64X1        | Primitive: 64-Deep by 1-Wide ROM                                                        |

| ROM128X1       | Primitive: 128-Deep by 1-Wide ROM                                                       |

| ROM256X1       | Primitive: 256-Deep by 1-Wide ROM                                                       |

# **Registers & Latches**

| Design Element | Description                                                                                       |

|----------------|---------------------------------------------------------------------------------------------------|

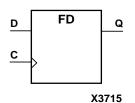

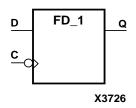

| FD             | Primitive: D Flip-Flop                                                                            |

| FD_1           | Primitive: D Flip-Flop with Negative-Edge Clock                                                   |

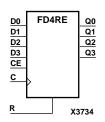

| FD4CE          | Macro: 4-Bit Data Register with Clock Enable and Asynchronous Clear                               |

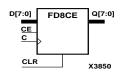

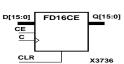

| FD8CE          | Macro: 8-Bit Data Register with Clock Enable and Asynchronous Clear                               |

| FD16CE         | Macro: 16-Bit Data Register with Clock Enable and Asynchronous Clear                              |

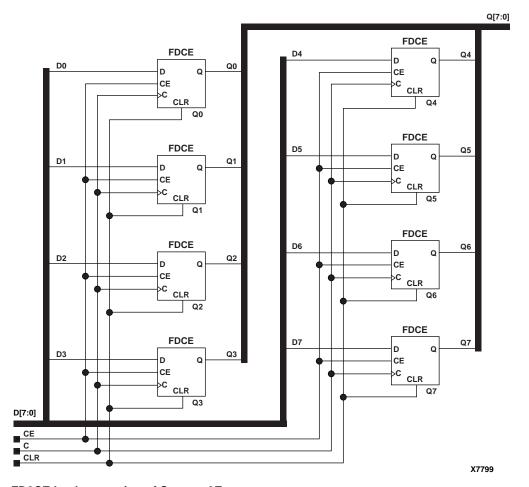

| FD4RE          | Macro: 4-Bit Data Register with Clock Enable and Synchronous Reset                                |

| FD8RE          | Macro: 8-Bit Data Register with Clock Enable and Synchronous Reset                                |

| FD16RE         | Macro: 16-Bit Data Register with Clock Enable and Synchronous Reset                               |

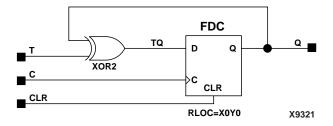

| FDC            | Primitive : D Flip-Flop with Asynchronous Clear                                                   |

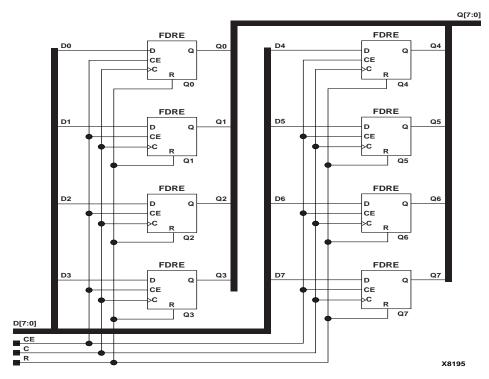

| FDC_1          | Primitive : D Flip-Flop with Negative-Edge Clock and Asynchronous Clear                           |

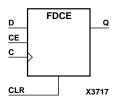

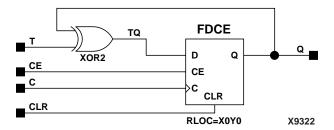

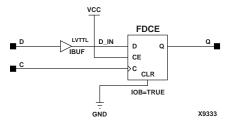

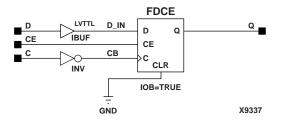

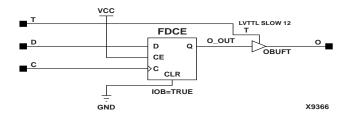

| FDCE           | Primitive : D Flip-Flop with Clock Enable and Asynchronous Clear                                  |

| FDCE_1         | Primitive : D Flip-Flop with Negative-Edge Clock, Clock Enable, and Asynchronous Clear            |

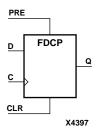

| FDCP           | Primitive : D Flip-Flop with Asynchronous Preset and Clear                                        |

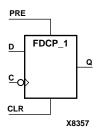

| FDCP_1         | Primitive : D Flip-Flop with Negative-Edge Clock and Asynchronous Preset and Clear                |

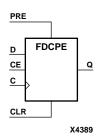

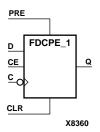

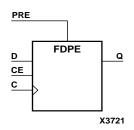

| FDCPE          | Primitive : D Flip-Flop with Clock Enable and Asynchronous Preset and Clear                       |

| FDCPE_1        | Primitive : D Flip-Flop with Negative-Edge Clock, Clock Enable, and Asynchronous Preset and Clear |

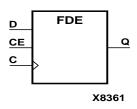

| FDE            | Primitive : D Flip-Flop with Clock Enable                                                         |

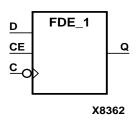

| FDE_1          | Primitive : D Flip-Flop with Negative-Edge Clock and Clock Enable                                 |

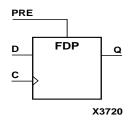

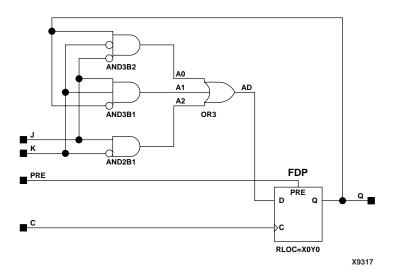

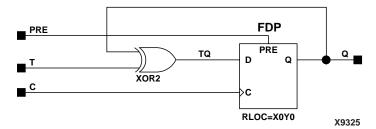

| FDP            | Primitive : D Flip-Flop with Asynchronous Preset                                                  |

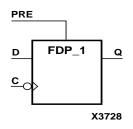

| FDP_1          | Primitive : D Flip-Flop with Negative-Edge Clock and Asynchronous Preset                          |

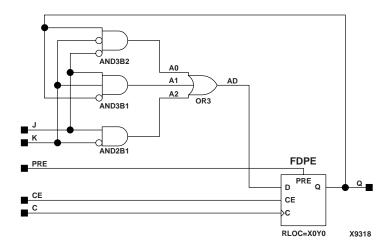

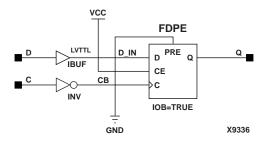

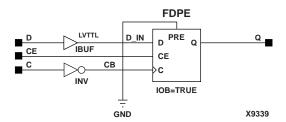

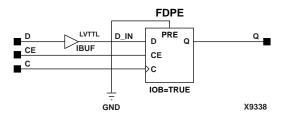

| FDPE           | Primitive : D Flip-Flop with Clock Enable and Asynchronous Preset                                 |

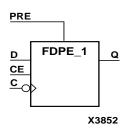

| FDPE_1         | Primitive : D Flip-Flop with Negative-Edge Clock, Clock Enable, and Asynchronous Preset           |

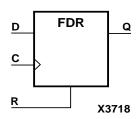

| FDR            | Primitive : D Flip-Flop with Synchronous Reset                                                    |

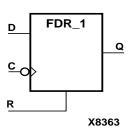

| FDR_1          | Primitive : D Flip-Flop with Negative-Edge Clock and Synchronous Reset                            |

| FDRE           | Primitive : D Flip-Flop with Clock Enable and Synchronous Reset                                   |

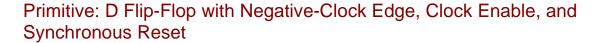

| FDRE_1         | Primitive : D Flip-Flop with Negative-Clock Edge, Clock Enable, and Synchronous Reset             |

| Design Element | Description                                                                                   |

|----------------|-----------------------------------------------------------------------------------------------|

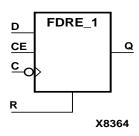

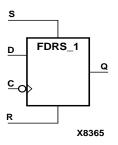

| FDRS           | Primitive : D Flip-Flop with Synchronous Reset and Set                                        |

| FDRS_1         | Primitive : D Flip-Flop with Negative-Clock Edge and Synchronous Reset and Set                |

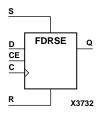

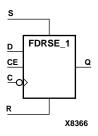

| FDRSE          | Primitive : D Flip-Flop with Synchronous Reset and Set and Clock Enable                       |

| FDRSE_1        | Primitive : D Flip-Flop with Negative-Clock Edge, Synchronous Reset and Set, and Clock Enable |

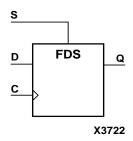

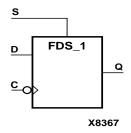

| FDS            | Primitive : D Flip-Flop with Synchronous Set                                                  |

| FDS_1          | Primitive : D Flip-Flop with Negative-Edge Clock and Synchronous Set                          |

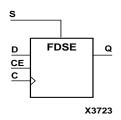

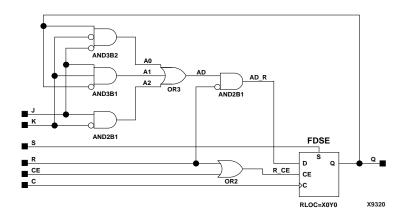

| FDSE           | Primitive : D Flip-Flop with Clock Enable and Synchronous Set                                 |

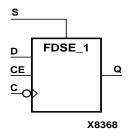

| FDSE_1         | Primitive : D Flip-Flop with Negative-Edge Clock, Clock Enable, and Synchronous Set           |

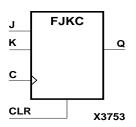

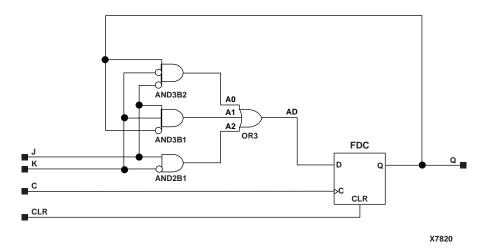

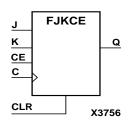

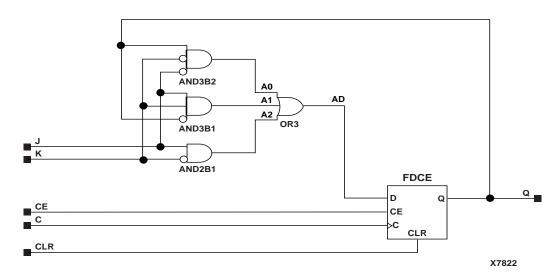

| FJKC           | Macro : J-K Flip-Flop with Asynchronous Clear                                                 |

| FJKCE          | Macro : J-K Flip-Flop with Clock Enable and Asynchronous Clear                                |

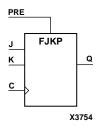

| FJKP           | Macro : J-K Flip-Flop with Asynchronous Preset                                                |

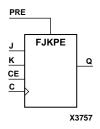

| FJKPE          | Macro : J-K Flip-Flop with Clock Enable and Asynchronous Preset                               |

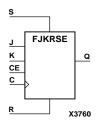

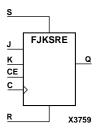

| FJKRSE         | Macro : J-K Flip-Flop with Clock Enable and Synchronous Reset and Set                         |

| FJKSRE         | Macro : J-K Flip-Flop with Clock Enable and Synchronous Set and Reset                         |

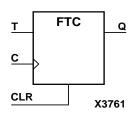

| FTC            | Macro : Toggle Flip-Flop with Toggle Enable and Asynchronous Clear                            |

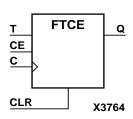

| FTCE           | Macro : Toggle Flip-Flop with Toggle and Clock Enable and Asynchronous Clear                  |

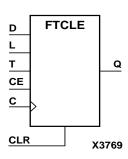

| FTCLE          | Macro : Toggle/Loadable Flip-Flop with Toggle and Clock Enable and Asynchronous Clear         |

| FTCLEX         | Macro : Toggle/Loadable Flip-Flop with Toggle and Clock Enable and Asynchronous Clear         |

| FTP            | Macro : Toggle Flip-Flop with Toggle Enable and Asynchronous Preset                           |

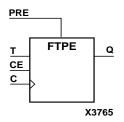

| FTPE           | Macro : Toggle Flip-Flop with Toggle and Clock Enable and Asynchronous Preset                 |

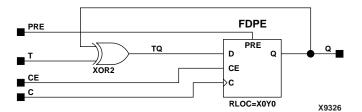

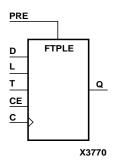

| FTPLE          | Macro : Toggle/Loadable Flip-Flop with Toggle and Clock Enable and Asynchronous Preset        |

| FTRSE          | Macro : Toggle Flip-Flop with Toggle and Clock Enable and Synchronous Reset and Set           |

| FTRSLE         | Macro : Toggle/Loadable Flip-Flop with Toggle and Clock Enable and Synchronous Reset and Set  |

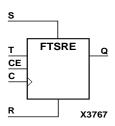

| FTSRE          | Macro : Toggle Flip-Flop with Toggle and Clock Enable and Synchronous Set and Reset           |

| FTSRLE         | Macro : Toggle/Loadable Flip-Flop with Toggle and Clock Enable and Synchronous Set and Reset  |

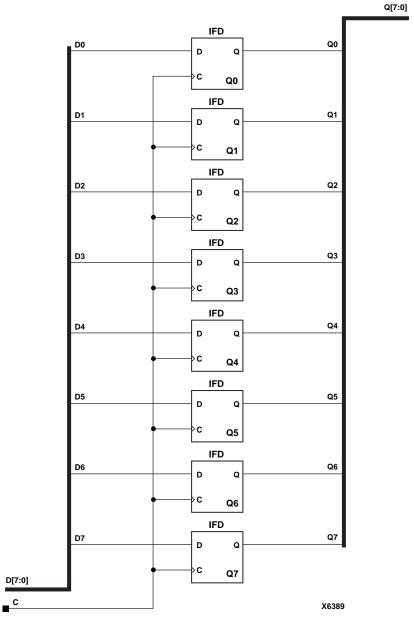

| IFD            | Macro : Single- and Multiple-Input D Flip-Flop                                                |

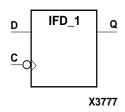

| IFD_1          | Macro : Input D Flip-Flop with Inverted Clock                                                 |

| IFD4           | Macro : Single- and Multiple-Input D Flip-Flop                                                |

| IFD8           | Macro : Single- and Multiple-Input D Flip-Flop                                                |

| IFD16          | Macro : Single- and Multiple-Input D Flip-Flop                                                |

| IFDI           | Macro : Input D Flip-Flop (Asynchronous Preset)                                               |

| IFDI_1         | Macro : Input D Flip-Flop with Inverted Clock (Asynchronous Preset)                           |

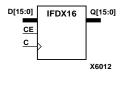

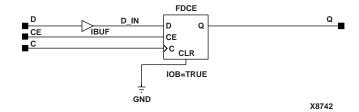

| IFDX           | Macro : Single- and Multiple-Input D Flip-Flop with Clock Enable                              |

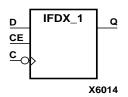

| IFDX_1         | Macro : Input D Flip-Flop with Inverted Clock and Clock Enable                                |

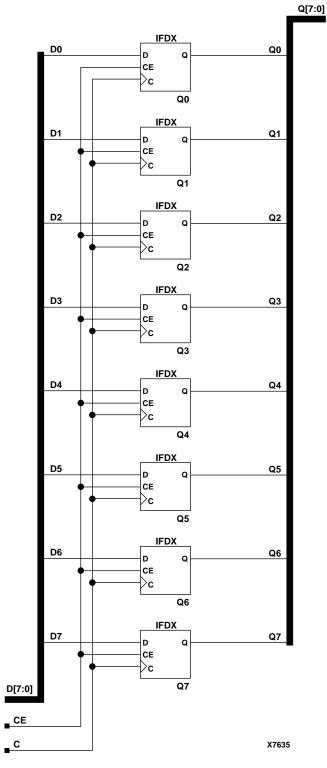

| IFDX4          | Macro : Single- and Multiple-Input D Flip-Flop with Clock Enable                              |

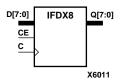

| IFDX8          | Macro : Single- and Multiple-Input D Flip-Flop with Clock Enable                              |

| IFDX16         | Macro : Single- and Multiple-Input D Flip-Flops with Clock Enable                             |

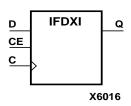

| IFDXI          | Macro : Input D Flip-Flop with Clock Enable (Asynchronous Preset)                             |

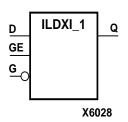

| ILDXI_1        | Macro: Input D Flip-Flop with Inverted Clock and Clock Enable (Asynchronous Preset)           |

| ILD            | Macro : Transparent Input Data Latch                                                          |

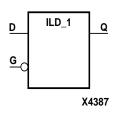

| ILD_1          | Macro : Transparent Input Data Latch with Inverted Gate                                       |

| ILD4           | Macro : Transparent Input Data Latch                                                          |

| ILD8           | Macro : Transparent Input Data Latch                                                          |

| ILD16          | Macro : Transparent Input Data Latch                                                          |

| ILDI           | Macro : Transparent Input Data Latch (Asynchronous Preset)                                    |

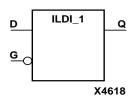

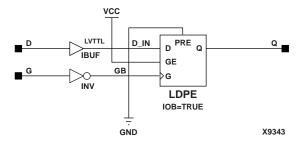

| ILDI_1         | Macro : Transparent Input Data Latch with Inverted Gate (Asynchronous Preset)                 |

| ILDX           | Macro : Transparent Input Data Latch                                                          |

| Design Element | Description                                                                                           |

|----------------|-------------------------------------------------------------------------------------------------------|

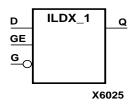

| ILDX_1         | Macro : Transparent Input Data Latch with Inverted Gate                                               |

| ILDX4          | Macro : Transparent Input Data Latch                                                                  |

| ILDX8          | Macro : Transparent Input Data Latch                                                                  |

| ILDX16         | Macro : Transparent Input Data Latch                                                                  |

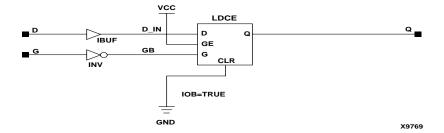

| ILDXI          | Macro : Transparent Input Data Latch (Asynchronous Preset)                                            |

| ILDXI_1        | Macro : Transparent Input Data Latch with Inverted Gate (Asynchronous Preset)                         |

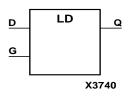

| LD             | Primitive : Transparent Data Latch                                                                    |

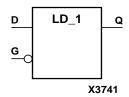

| LD_1           | Primitive : Transparent Data Latch with Inverted Gate                                                 |

| LD4            | Macro : Multiple Transparent Data Latch                                                               |

| LD8            | Macro : Multiple Transparent Data Latch                                                               |

| LD16           | Macro : Multiple Transparent Data Latch                                                               |

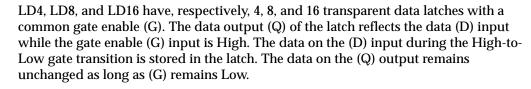

| LD4CE          | Macro : Transparent Data Latch with Asynchronous Clear and Gate Enable                                |

| LD8CE          | Macro : Transparent Data Latch with Asynchronous Clear and Gate Enable                                |

| LD16CE         | Macro : Transparent Data Latch with Asynchronous Clear and Gate Enable                                |

| LDC            | Primitive : Transparent Data Latch with Asynchronous Clear                                            |

| LDC_1          | Primitive : Transparent Data Latch with Asynchronous Clear and Inverted Gate                          |

| LDCE           | Primitive : Transparent Data Latch with Asynchronous Clear and Gate Enable                            |

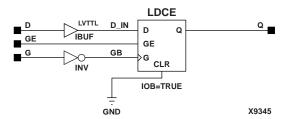

| LDCE_1         | Primitive : Transparent Data Latch with Asynchronous Clear, Gate Enable, and Inverted Gate            |

| LDCP           | Primitive : Transparent Data Latch with Asynchronous Clear and Preset                                 |

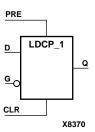

| LDCP_1         | Primitive : Transparent Data Latch with Asynchronous Clear and Preset and Inverted Gate               |

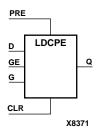

| LDCPE          | Primitive : Transparent Data Latch with Asynchronous Clear and Preset and Gate Enable                 |

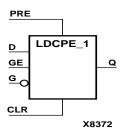

| LDCPE_1        | Primitive : Transparent Data Latch with Asynchronous Clear and Preset, Gate Enable, and Inverted Gate |

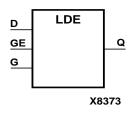

| LDE            | Primitive : Transparent Data Latch with Gate Enable                                                   |

| LDE_1          | Primitive : Transparent Data Latch with Gate Enable and Inverted Gate                                 |

| LDP            | Primitive : Transparent Data Latch with Asynchronous Preset                                           |

| LDP_1          | Primitive : Transparent Data Latch with Asynchronous Preset and Inverted Gate                         |

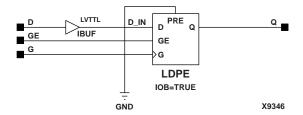

| LDPE           | Primitive : Transparent Data Latch with Asynchronous Preset and Gate Enable                           |

| LDPE_1         | Primitive : Transparent Data Latch with Asynchronous Preset, Gate Enable, and Inverted Gate           |

| OFD            | Macro : Single- and Multiple-Output D Flip-Flops                                                      |

| OFD_1          | Macro : Output D Flip-Flop with Inverted Clock                                                        |

| OFD4           | Macro : Single- and Multiple-Output D Flip-Flops                                                      |

| OFD8           | Macro : Single- and Multiple-Output D Flip-Flops                                                      |

| OFD16          | Macro : Single- and Multiple-Output D Flip-Flops                                                      |

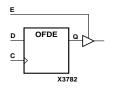

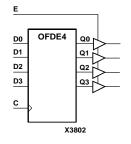

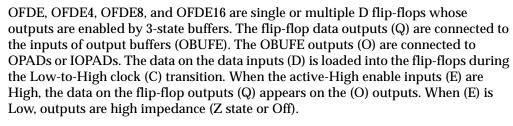

| OFDE           | Macro : D Flip-Flop with Active-High Enable Output Buffers                                            |

| OFDE_1         | Macro : D Flip-Flop with Active-High Enable Output Buffer and Inverted Clock                          |

| OFDE4          | Macro : D Flip-Flop with Active-High Enable Output Buffers                                            |

| OFDE8          | Macro : D Flip-Flop with Active-High Enable Output Buffers                                            |

| OFDE16         | Macro : D Flip-Flop with Active-High Enable Output Buffers                                            |

| OFDI           | Macro : Output D Flip-Flop (Asynchronous Preset)                                                      |

| OFDI_1         | Macro : Output D Flip-Flop with Inverted Clock (Asynchronous Preset)                                  |

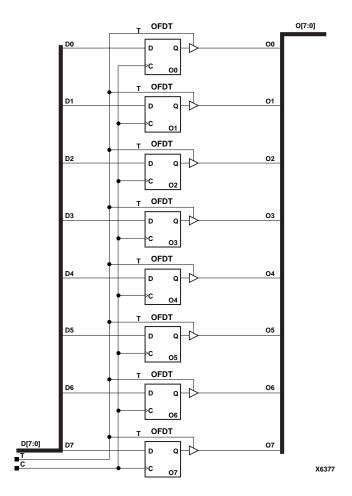

| OFDT           | Macro: Single and Multiple D Flip-Flop with Active-Low 3-State Output Buffers                         |

| OFDT_1         | Macro: D Flip-Flop with Active-Low 3-State Output Buffer and Inverted Clock                           |

| OFDT4          | Macro: Single and Multiple D Flip-Flop with Active-Low 3-State Output Buffers                         |

| OFDT8          | Macro: Single and Multiple D Flip-Flop with Active-Low 3-State Output Buffers                         |

| OFDT16         | Macro: Single and Multiple D Flip-Flop with Active-Low 3-State Output Buffers                         |

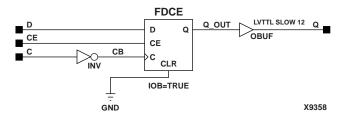

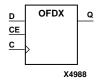

| OFDX           | Macro: Single- and Multiple-Output D Flip-Flop with Clock Enable                                      |

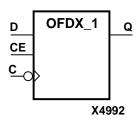

| OFDX_1         | Macro : Output D Flip-Flop with Inverted Clock and Clock Enable                                       |

| Design Element | Description                                                                           |

|----------------|---------------------------------------------------------------------------------------|

| OFDX4          | Macro : Single- and Multiple-Output D Flip-Flop with Clock Enable                     |

| OFDX8          | Macro : Single- and Multiple-Output D Flip-Flop with Clock Enable                     |

| OFDX16         | Macro : Single- and Multiple-Output D Flip-Flop with Clock Enable                     |

| OFDXI          | Macro : Output D Flip-Flop with Clock Enable (Asynchronous Preset)                    |

| OFDXI_1        | Macro : Output D Flip-Flop with Inverted Clock and Clock Enable (Asynchronous Preset) |

### **Shift Registers**

| Design Element | Description                                                                                                     |

|----------------|-----------------------------------------------------------------------------------------------------------------|

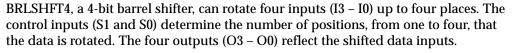

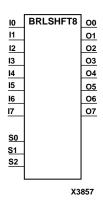

| BRLSHFT4       | Macro : 4-Bit Barrel Shifter                                                                                    |

| BRLSHFT8       | Macro: 8-Bit Barrel Shifter                                                                                     |

| SR4CE          | Macro : 4-Bit Serial-In Parallel-Out Shift Register with Clock Enable and Asynchronous Clear                    |

| SR8CE          | Macro : 8-Bit Serial-In Parallel-Out Shift Register with Clock Enable and Asynchronous Clear                    |

| SR16CE         | Macro : 16-Bit Serial-In Parallel-Out Shift Register with Clock Enable and Asynchronous Clear                   |

| SR4CLE         | Macro : 4-Bit Loadable Serial/Parallel-In Parallel-Out Shift Register with Clock Enable and Asynchronous Clear  |

| SR8CLE         | Macro : 8-Bit Loadable Serial/Parallel-In Parallel-Out Shift Register with Clock Enable and Asynchronous Clear  |

| SR16CLE        | Macro : 16-Bit Loadable Serial/Parallel-In Parallel-Out Shift Register with Clock Enable and Asynchronous Clear |

| SR4CLED        | Macro : 4-Bit Shift Register with Clock Enable and Asynchronous Clear                                           |

| SR8CLED        | Macro : 8-Bit Shift Register with Clock Enable and Asynchronous Clear                                           |

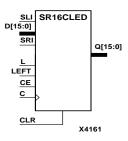

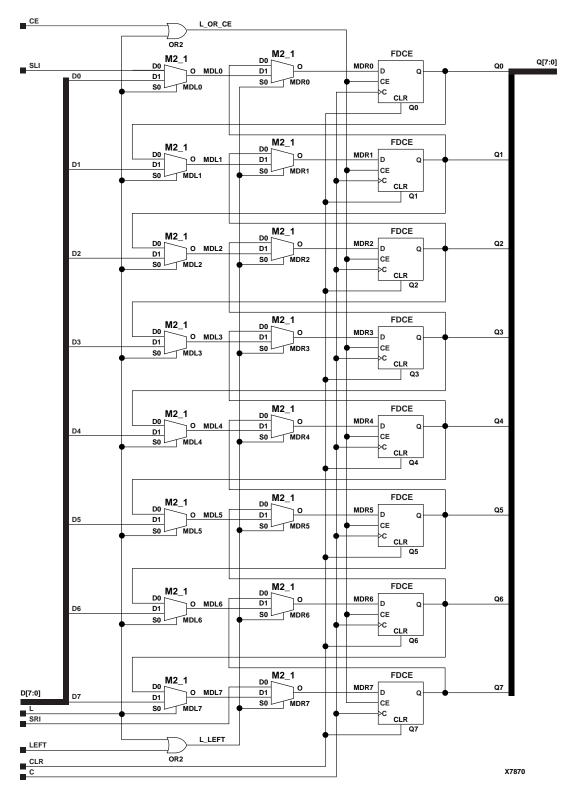

| SR16CLED       | Macro : 16-Bit Shift Register with Clock Enable and Asynchronous Clear                                          |

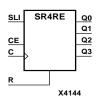

| SR4RE          | Macro : 4-Bit Serial-In Parallel-Out Shift Register with Clock Enable and Synchronous Reset                     |

| SR8RE          | Macro : 8-Bit Serial-In Parallel-Out Shift Register with Clock Enable and Synchronous Reset                     |

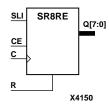

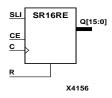

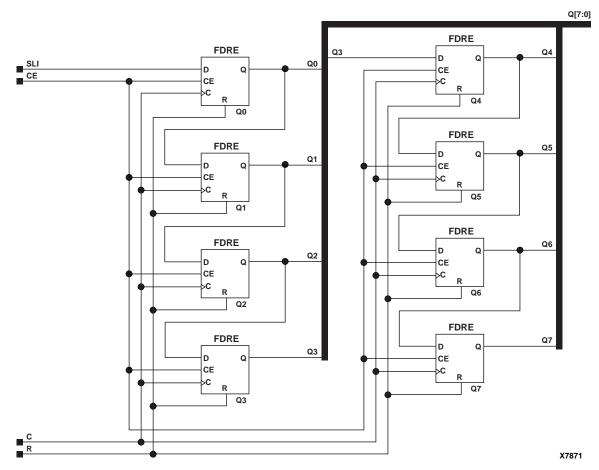

| SR16RE         | Macro : 16-Bit Serial-In Parallel-Out Shift Register with Clock Enable and Synchronous Reset                    |

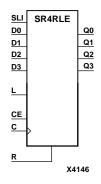

| SR4RLE         | Macro : 4-Bit Loadable Serial/Parallel-In Parallel-Out Shift Register with Clock Enable and Synchronous Reset   |

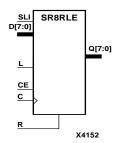

| SR8RLE         | Macro : 8-Bit Loadable Serial/Parallel-In Parallel-Out Shift Register with Clock Enable and Synchronous Reset   |

| SR16RLE        | Macro : 16-Bit Loadable Serial/Parallel-In Parallel-Out Shift Register with Clock Enable and Synchronous Reset  |

| SR4RLED        | Macro : 4-Bit Shift Register with Clock Enable and Synchronous Reset                                            |

| SR8RLED        | Macro : 8-Bit Shift Register with Clock Enable and Synchronous Reset                                            |

| SR16RLED       | Macro : 16-Bit Shift Register with Clock Enable and Synchronous Reset                                           |

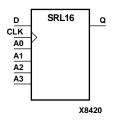

| SRL16          | Primitive : 16-Bit Shift Register Look-Up-Table (LUT)                                                           |

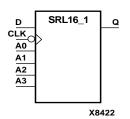

| SRL16_1        | Primitive : 16-Bit Shift Register Look-Up-Table (LUT) with Negative-Edge Clock                                  |

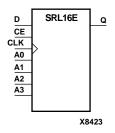

| SRL16E         | Primitive : 16-Bit Shift Register Look-Up-Table (LUT) with Clock Enable                                         |

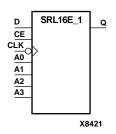

| SRL16E_1       | Primitive : 16-Bit Shift Register Look-Up-Table (LUT) with Negative-Edge Clock and Clock Enable                 |

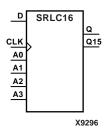

| SRLC16         | Primitive : 16-Bit Shift Register Look-Up-Table (LUT) with Carry                                                |

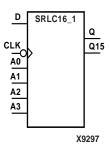

| SRLC16_1       | Primitive : 16-Bit Shift Register Look-Up-Table (LUT) with Carry and Negative-Edge Clock                        |

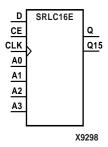

| SRLC16E        | Primitive : 16-Bit Shift Register Look-Up-Table (LUT) with Carry and Clock Enable                               |

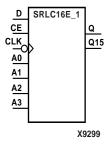

| SRLC16E_1      | Primitive : 16-Bit Shift Register Look-Up-Table (LUT) with Carry, Negative-Edge Clock, and Clock Enable         |

### **Slice/CLB Primitives**

| Design Element | Description                                         |

|----------------|-----------------------------------------------------|

| LUT1           | Primitive : 1-Bit Look-Up-Table with General Output |

| LUT2           | Primitive : 2-Bit Look-Up-Table with General Output |

| LUT3           | Primitive : 3-Bit Look-Up-Table with General Output |

| LUT4           | Primitive : 4-Bit Look-Up-Table with General Output |

| LUT1_D         | Primitive : 1-Bit Look-Up-Table with Dual Output    |

| LUT2_D         | Primitive : 2-Bit Look-Up-Table with Dual Output    |

| Design Element | Description                                                        |

|----------------|--------------------------------------------------------------------|

| LUT3_D         | Primitive : 3-Bit Look-Up-Table with Dual Output                   |

| LUT4_D         | Primitive : 4-Bit Look-Up-Table with Dual Output                   |

| LUT1_L         | Primitive : 1-Bit Look-Up-Table with Local Output                  |

| LUT2_L         | Primitive : 2-Bit Look-Up-Table with Local Output                  |

| LUT3_L         | Primitive : 3-Bit Look-Up-Table with Local Output                  |

| LUT4_L         | Primitive : 4-Bit Look-Up-Table with Local Output                  |

| MULT_AND       | Primitive : Fast Multiplier AND                                    |

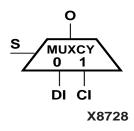

| MUXCY          | Primitive : 2-to-1 Multiplexer for Carry Logic with General Output |

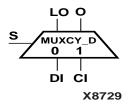

| MUXCY_D        | Primitive : 2-to-1 Multiplexer for Carry Logic with Dual Output    |

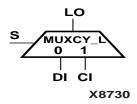

| MUXCY_L        | Primitive : 2-to-1 Multiplexer for Carry Logic with Local Output   |

| MUXF5          | Primitive : 2-to-1 Lookup Table Multiplexer with General Output    |

| MUXF5_D        | Primitive : 2-to-1 Lookup Table Multiplexer with Dual Output       |

| MUXF5_L        | Primitive : 2-to-1 Lookup Table Multiplexer with Local Output      |

| MUXF6          | Primitive : 2-to-1 Lookup Table Multiplexer with General Output    |

| MUXF6_D        | Primitive : 2-to-1 Lookup Table Multiplexer with Dual Output       |

| MUXF6_L        | Primitive : 2-to-1 Lookup Table Multiplexer with Local Output      |

| MUXF7          | Primitive : 2-to-1 Lookup Table Multiplexer with General Output    |

| MUXF7_D        | Primitive : 2-to-1 Lookup Table Multiplexer with Dual Output       |

| MUXF7_L        | Primitive : 2-to-1 Lookup Table Multiplexer with Local Output      |

| MUXF8          | Primitive : 2-to-1 Lookup Table Multiplexer with General Output    |

| MUXF8_D        | Primitive : 2-to-1 Lookup Table Multiplexer with Dual Output       |

| MUXF8_L        | Primitive : 2-to-1 Lookup Table Multiplexer with Local Output      |

| XORCY          | Primitive : XOR for Carry Logic with General Output                |

| XORCY_D        | Primitive : XOR for Carry Logic with Dual Output                   |

| XORCY_L        | Primitive : XOR for Carry Logic with Local Output                  |

# About the Spartan-3E Design Elements

The remaining sections in this book describe each primitive design element that can be used under the Spartan-3E architecture.

The design elements are organized in alphanumeric order, with all numeric suffixes in ascending order. For example, FDCPE precedes FDRSE, and IBUF precedes IBUFDS.

The following information is provided for each library element, where applicable

- · Name of each element

- Description of each element, including truth tables, where applicable

- A description of the attributes associated with each design element, where appropriate.

- Referrals to additional sources of information.

Designers who prefer to work with hardware description language (HDL) are encouraged to consult the *Spartan-3E Libraries Guide for HDL Designs*.

### ACC4, 8, 16

### Macro: 4-, 8-, 16-Bit Loadable Cascadable Accumulators with Carry-In, Carry-Out, and Synchronous Reset

ACC4, ACC8, ACC16 can add or subtract a 4-, 8-, 16-bit unsigned-binary, respectively or twos-complement word to or from the contents of a 4-, 8-, 16-bit data register and store the results in the register. The register can be loaded with the 4-, 8-, 16-bit word.

The synchronous reset (R) has priority over all other inputs, and when High, causes all outputs to go to logic level zero during the Low-to-High clock (C) transition. Clock (C) transitions are ignored when clock enable (CE) is Low.

The accumulator is asynchronously cleared, outputs Low, when power is applied.

Spartan-3E simulates power-on when global set/reset (GSR) is active.

GSR defaults to active-High but can be inverted by adding an inverter in front of the GSR input of the STARTUP\_SPARTAN3E symbol.

### Load

When the load input (L) is High, CE is ignored and the data on the D inputs is loaded into the register during the Low-to-High clock (C) transition. ACC4 loads the data on inputs D3 - D0 into the 4-bit register. ACC8 loads the data on D7 - D0 into the 8-bit register. ACC16 loads the data on inputs D15 – D0 into the 16-bit register.

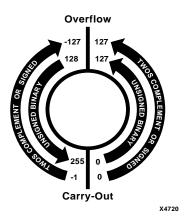

### **Unsigned Binary Versus Twos Complement**

Q[15:0] B[15:0] CO D[15:0] L OFL A<u>DD</u> CE X4375

ACC4, ACC8, ACC16 can operate, respectively, on either 4-, 8-, 16-bit unsigned binary numbers or 4-, 8-, 16-bit twos-complement numbers. If the inputs are interpreted as unsigned binary, the result can be interpreted as unsigned binary. If the inputs are interpreted as two complement, the output can be interpreted as two complement. The only functional difference between an unsigned binary operation and a twoscomplement operation is how they determine when "overflow" occurs. Unsigned binary uses CO, while twos complement uses OFL to determine when "overflow" occurs.

### Unsigned Binary Operation

For unsigned binary operation, ACC4 can represent numbers between 0 and 15, inclusive; ACC8 between 0 and 255, inclusive; and ACC16 between 0 and 65535, inclusive. In add mode, CO is active (High) when the sum exceeds the bounds of the adder/subtracter. In subtract mode, CO is an active-Low borrow-out and goes Low when the difference exceeds the bounds. The carry-out (CO) is not registered synchronously with the data outputs. CO always reflects the accumulation of the B inputs (B3 - B0 for ACC4, B7 - B0 for ACC8, B15 - B0 for ACC16) and the contents of the register. This allows cascading of ACC4s, ACC8s, or ACC16s by connecting CO of one stage to CI of the next stage. An unsigned binary "overflow" that is always active-High can be generated by gating the ADD signal and CO as follows.

unsigned overflow = CO XOR ADD

Ignore OFL in unsigned binary operation.

### Twos-Complement Operation

For twos-complement operation, ACC4 can represent numbers between -8 and +7, inclusive; ACC8 between -128 and +127, inclusive; ACC16 between -32768 and +32767, inclusive. If an addition or subtraction operation result exceeds this range, the OFL output goes High. The overflow (OFL) is not registered synchronously with the data outputs. OFL always reflects the accumulation of the B inputs (B3 - B0 for ACC4, B7 - B0 for ACC8, B15 - B0 for ACC16) and the contents of the register, which allows cascading of ACC4s, ACC8s, or ACC16s by connecting OFL of one stage to CI of the next stage.

Ignore CO in twos-complement operation.

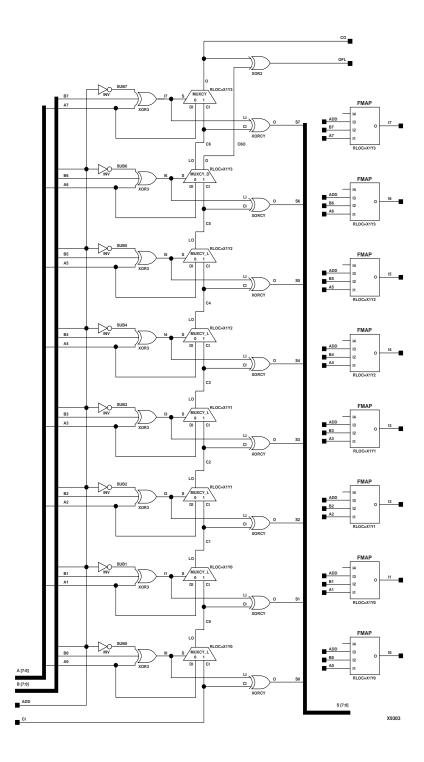

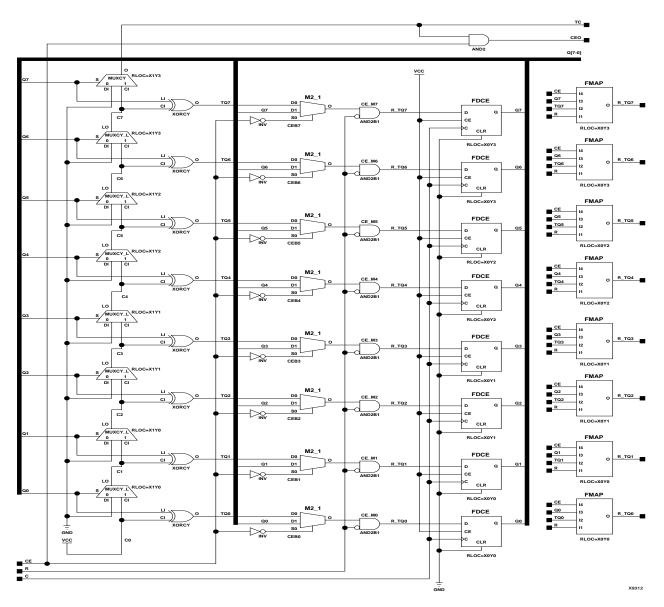

**ACC8 Implementation for Spartan-3E**

Usage

ACC is intended for schematics only.

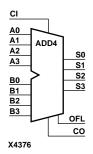

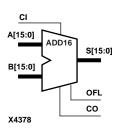

### ADD4, 8, 16

# Macro: 4-, 8-, 16-Bit Cascadable Full Adders with Carry-In, Carry-Out, and Overflow

ADD4, ADD8, and ADD16 add two words and a carry-in (CI), producing a sum output and carry-out (CO) or overflow (OFL). ADD4 adds A3 - A0, B3 - B0, and CI producing the sum output S3 - S0 and CO (or OFL). ADD8 adds A7 - A0, B7 - B0, and CI, producing the sum output S7 - S0 and CO (or OFL). ADD16 adds A15 - A0, B15 - B0 and CI, producing the sum output S15 - S0 and CO (or OFL).

### **Unsigned Binary Versus Twos Complement**

ADD4, ADD8, ADD16 can operate on either 4-, 8-, 16-bit unsigned binary numbers or 4-, 8-, 16-bit twos-complement numbers, respectively. If the inputs are interpreted as unsigned binary, the result can be interpreted as unsigned binary. If the inputs are interpreted as twos complement, the output can be interpreted as twos complement. The only functional difference between an unsigned binary operation and a twoscomplement operation is how they determine when "overflow" occurs. Unsigned binary uses CO, while twos-complement uses OFL to determine when "overflow" occurs. To interpret the inputs as unsigned binary, follow the CO output. To interpret the inputs as twos complement, follow the OFL output.

### **Unsigned Binary Operation**

For unsigned binary operation, ADD4 can represent numbers between 0 and 15, inclusive; ADD8 between 0 and 255, inclusive; ADD16 between 0 and 65535, inclusive. CO is active (High) when the sum exceeds the bounds of the adder.

OFL is ignored in unsigned binary operation.

### Twos-Complement Operation

For twos-complement operation, ADD4 can represent numbers between -8 and +7, inclusive; ADD8 between -128 and +127, inclusive; ADD16 between -32768 and +32767, inclusive. OFL is active (High) when the sum exceeds the bounds of the adder. CO is ignored in twos-complement operation.

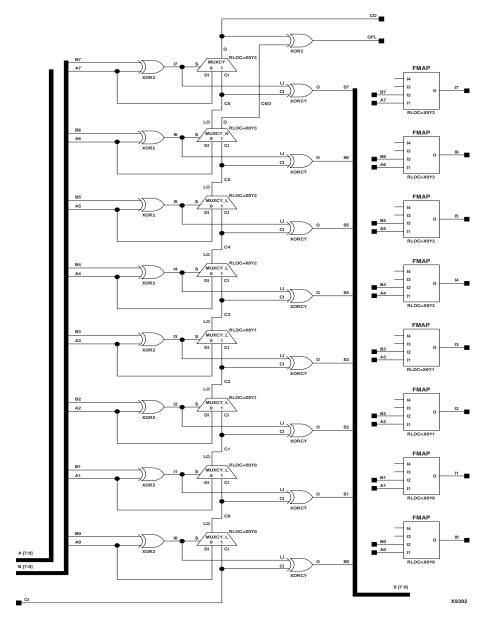

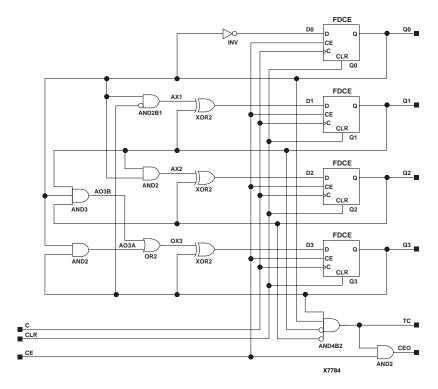

**ADD8 Implementation Spartan-3E**

### Usage

This design element is a schematic only.

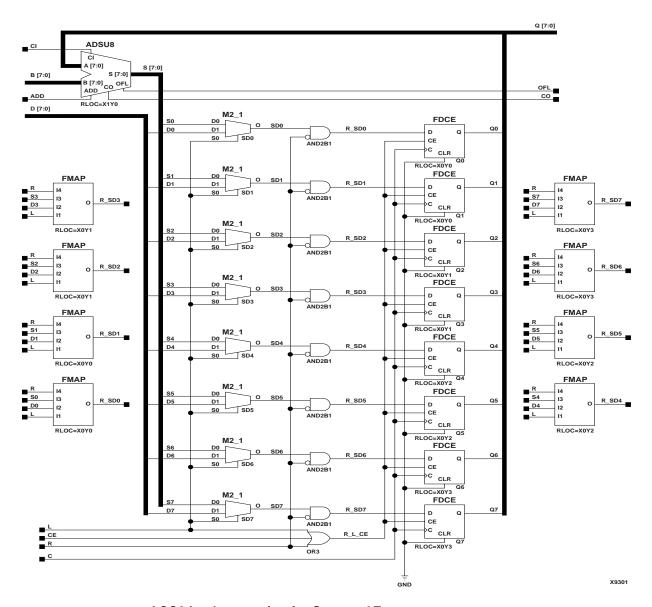

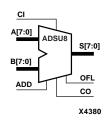

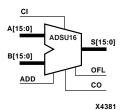

### **ADSU4, 8, 16**

### Macro: 4-, 8-, 16-Bit Cascadable Adders/Subtracters with Carry-In, Carry-Out, and Overflow

When the ADD input is High, ADSU4, ADSU8, and ADSU16 add two words and a carry-in (CI), producing a sum output and carry-out (CO) or overflow (OFL). ADSU4 adds two 4-bit words (A3 - A0 and B3 - B0) and a CI, producing a 4-bit sum output (S3 - S0) and CO or OFL. ADSU8 adds two 8-bit words (A7 - A0 and B7 - B0) and a CI producing, an 8-bit sum output (S7 – S0) and CO or OFL. ADSU16 adds two 16-bit words (A15 - A0 and B15 - B0) and a CI, producing a 16-bit sum output (S15 - S0) and CO or OFL.

When the ADD input is Low, ADSU4, ADSU8, and ADSU16 subtract Bz – B0 from Az-A0, producing a difference output and CO or OFL. ADSU4 subtracts B3 - B0 from A3 - A0, producing a 4-bit difference (S3 - S0) and CO or OFL. ADSU8 subtracts B7 -B0 from A7 - A0, producing an 8-bit difference (S7 - S0) and CO or OFL. ADSU16 subtracts B15 - B0 from A15 - A0, producing a 16-bit difference (S15 - S0) and CO or OFL.

In add mode, CO and CI are active-High. In subtract mode, CO and CI are active-Low. OFL is active-High in add and subtract modes.

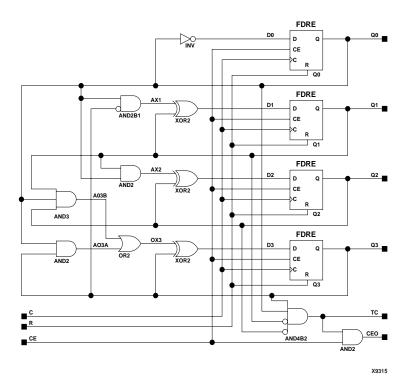

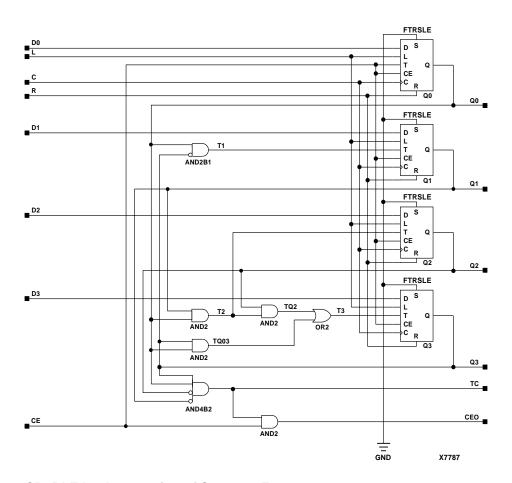

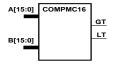

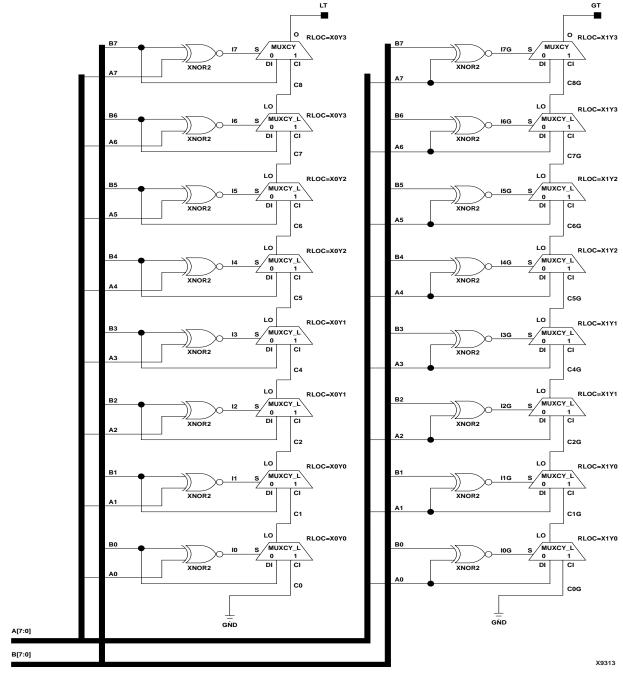

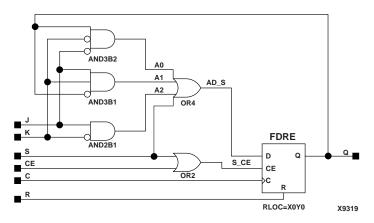

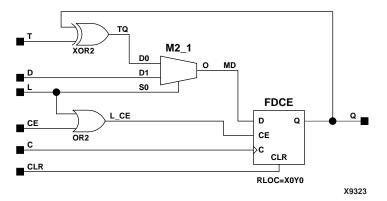

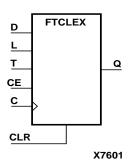

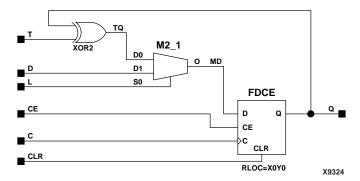

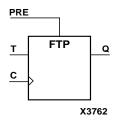

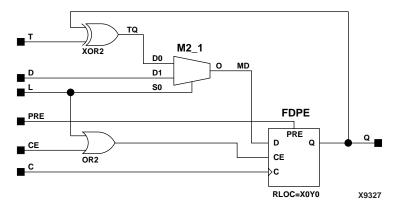

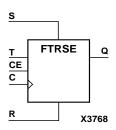

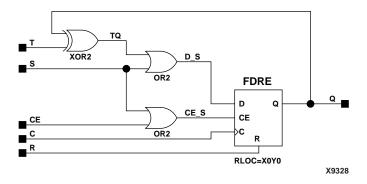

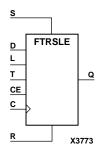

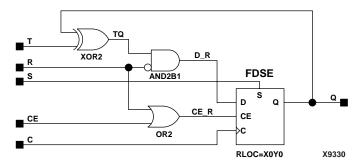

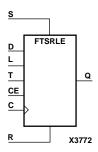

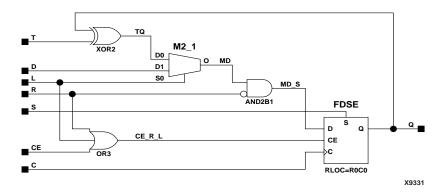

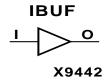

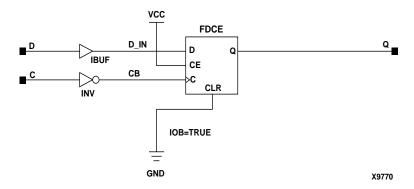

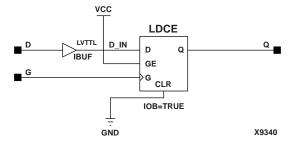

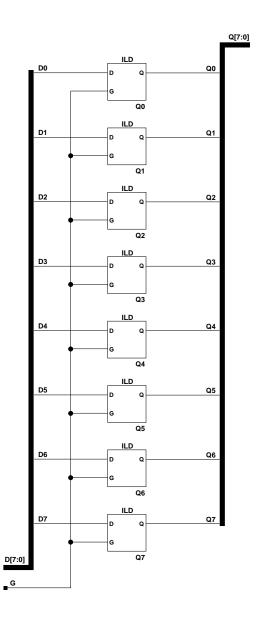

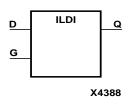

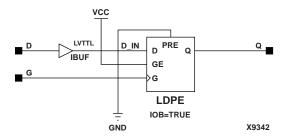

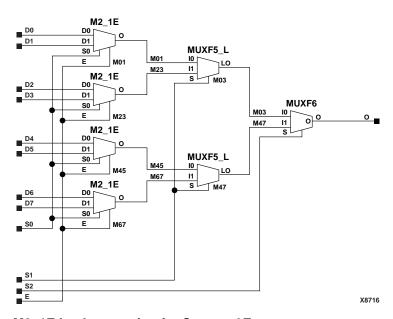

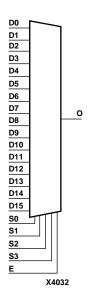

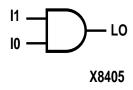

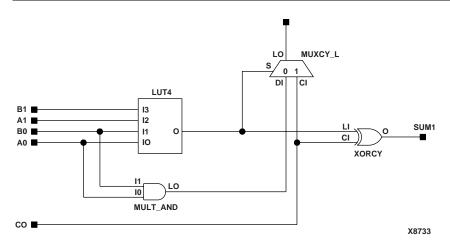

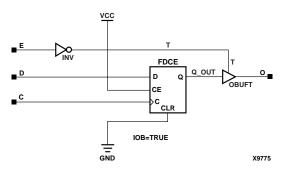

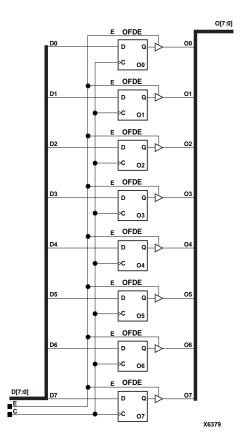

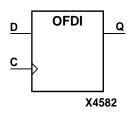

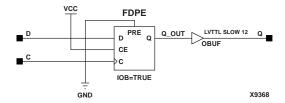

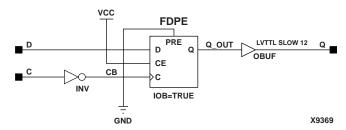

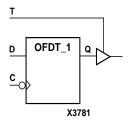

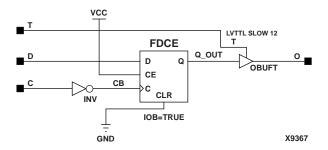

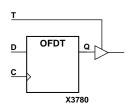

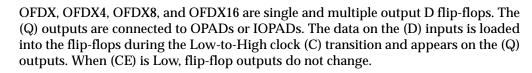

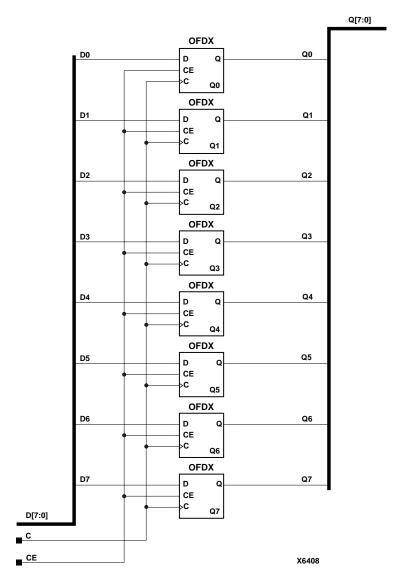

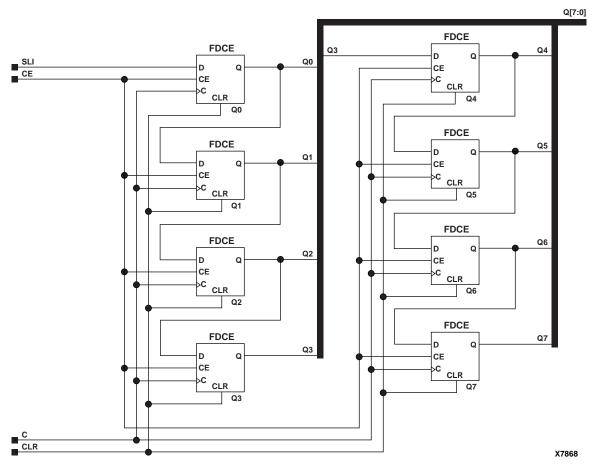

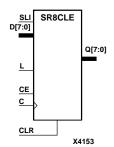

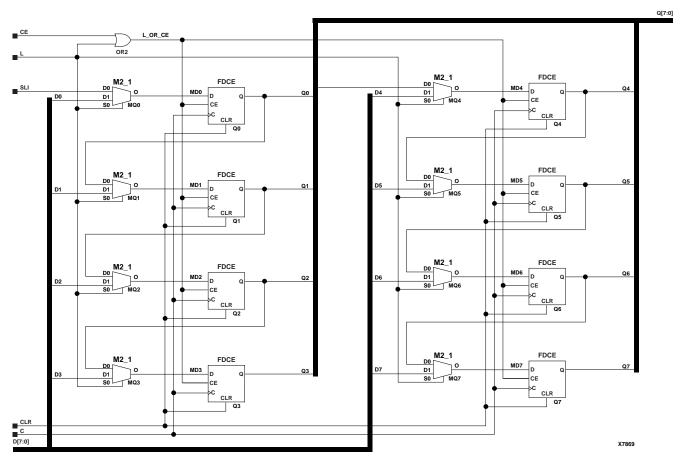

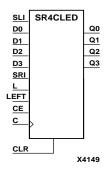

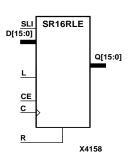

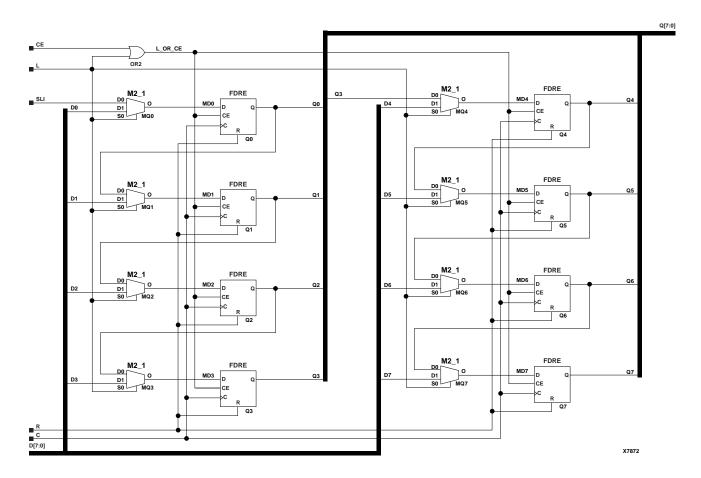

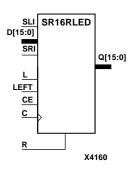

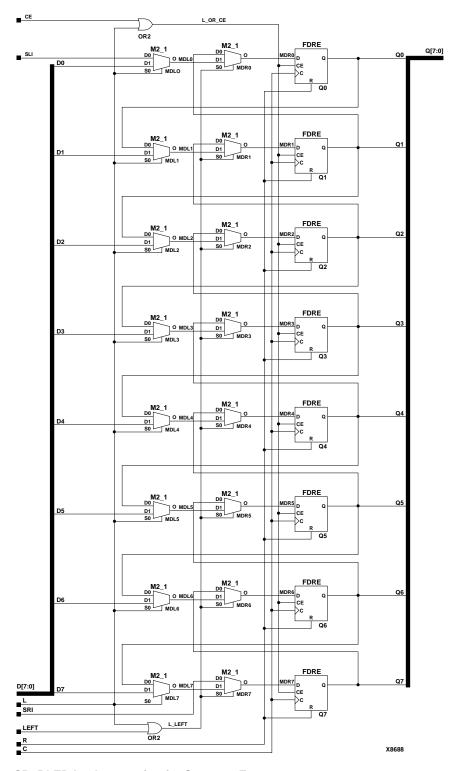

### Unsigned Binary Versus Twos Complement